# Chapter 1

## Introduction\*

### 1.1 Background and Objectives

The PARKBENCH (PARallel Kernels and BENCHmarks) committee, originally called the Parallel Benchmark Working Group. PBWG, was founded at Supercomputing 92 in Minneapolis, when a group of about 50 people interested in computer benchmarking met under the joint initiative of Tony Hey (University of Southampton, UK) and Jack Dongarra (University of Tennessee/Oak Ridge National Laboratory). Most of the key players were present, from the Universities. Laboratories and industries, representing both computer manufacturers and computer users from both sides of the Atlantic, Roger Hockney (University of Southampton) chaired the meeting, and the objectives of the group were:

- 1. To establish a comprehensive set of parallel benchmarks that is generally accepted by both users and vendors of parallel systems.

- To provide a focus for parallel benchmark activities and avoid unnecessary duplication of effort and proliferation of benchmarks.

- 3. To set standards for benchmarking methodology and result-reporting together with a control database/repository for both the benchmarks and the results.

- 4. To make the benchmarks and results freely available in the public domain.

The first year's work was to produce a report and an initial set of benchmarks for release at Supercomputing 93 in Portland, Oregon, November

1993. The committee has met at the University of Tennessee at Knoxville on March 1-2. 1993. May 24. 1993 and August 23. 1993 to discuss the evolving draft of this report. The document reproduced here is the final result of these meetings, and is the first official publication of the PARKBENCH committee. It was distributed at a public Birds of a Feather meeting at Supercomputing'93. Portland. on 17th November 1993. as a University of Tennessee Technical Report CS-93-213 [1]. The bulk of this publication in Scientific Programming differs only in non-substantive editorial ways from the technical report. An Appendix C has been added, however, containing selected results from the benchmarks. The first release of the PARKBENCH parallel benchmarks is available publicly over Internet.

The initial focus of the parallel benchmarks is on the new generation of scalable distributedmemory message-passing architectures for which there is a notable lack of existing benchmarks. For this reason the initial benchmark release concentrates on Fortran 77 message-passing codes using the widely available PVM [2] message passing interface for portability. Future versions will undoubtedly adopt the proposed MPI [3] interface. when this is fully defined and becomes generally accepted. The committee's aim. however, is to cover all parallel architectures, and this is expected to be achieved by producing versions of the benchmark codes using Fortran90 and High Performance Fortran (HPF). Many shared-memory architectures provide efficient native implementations of PVM message-passing and are planning HPF compilers. They will be covered by these routes.

## 1.2 Procedures

The PARKBENCH committee divides its work between five subcommittees, corresponding to the

Received November 1993 Accepted February 1994

© 1994 by John Wiley & Sons. Inc. Scientific Programming. Vol. 3, pp. 101–146 (1994) CCC 1058-9244/94/020101-46

<sup>\*</sup> Assembled by Roger Hockney for whole committee.

five substantive chapters in the report, each with a leader (shown in parentheses) who is responsible for assembling the contents of his chapter and its benchmarks for the committee's approval.

- 1. Chapter-2: Methodology (David Bailey):

- 2. Chapter-3: Low-level benchmarks (Roger Hockney):

- 3. Chapter-4: Kernel benchmarks (Tony Hey):

- 4. Chapter-5: Compact applications (David Walker):

- 5. Chapter-6: Compiler benchmarks (Tom Haupt):

In order to facilitate discussion and exchange of information, the following e-mail addresses were set up.

- 1. pbwg-comm@cs.utk.edu for the Whole committee

- 2. pbwg-method@cs.utk.edu for the Methodology subcommittee

- pbwg-lowlevel@cs.utk.edu for the Low level subcommittee

- pbwg-kernel@cs.utk.edu for the Kernel subcommittee

- 5. pbwg-compactapp@cs.utk.edu for the Compact applications subcommittee

Recent practice, however, has been to send all mail to pbwg-comm so that all members may see it. All mail is being collected and can be retrieved by sending email to netlib@ornl.gov and in the mail message typing:

- 1. send comm.archive from pbwg

- 2. send index from pbwg

- 3. send method archive from pbwg

- 4. send lowlevel.archive from plwg

- 5. send kernel.archive from pbwg

- 6. send compactapp.archive from pbwg

We have setup a mail reflector for correspondence, it is called pbwg-comm@cs.utk.edu. Mail to that address will be sent to the mailing list and also collected in netlib@ornl.gov. All PARKBENCH correspondence and benchmarks may be retrieved via anonymous ftp to netlib2.cs.utk.edu. Alternatively, one can collect PARKBENCH mail by sending email to netlib@ornl.gov and in the mail message type:

send comm.archive from pbwg

The PARKBENCH committee is open without charge to anyone interested in computer benchmarking and operates similarly to the HPFF (High Performance Fortran Forum). Anyone interested in joining in the discussion or preparing benchmarks should send e-mail to that effect to:

dongarra@cs.utk.edu

#### 1.3 Vendor's Commitment

The PARKBENCH committee is anxious that its parallel benchmarks do not put undue demands on computer vendors by way of man-power and resources. in a way that would prejudice the wide acceptance and use of the benchmarks. Initially it is felt reasonable to expect that most vendors should have little difficulty in running the lowlevel and kernel benchmarks, since these either involve basic hardware and software tests (such as COMMS1, see section 3.3.1) that vendors would wish to perform in any case, or involve scientific library subroutines (such as FFT, see section 4.2.2) that they would be required to produce and optimise. In the latter case, they would no doubt be pleased to show the superior performance of their library routine compared with that of the standard Fortran provided in the PARKBENCH benchmark suite.

The case of compact applications, which are stripped down complete application codes (see Chapter 5), is more difficult because these codes might require substantial effort to optimise, and in some cases even to run satisfactorily. For these reasons, it is not expected that vendors would initially run all these codes. They might, however, choose to run a selection of them from subject areas of interest to their current potential customers, in order to demonstrate their computer's capability on some standard and relevant tests. In this way, and over a period of time, it is hoped that most of the compact applications would be run in a natural way and without extra effort.

### 1.4 Programming Models

Computer benchmarks are computer programs that form standard tests of the performance of a computer and the software through which it is used. They are written to a particular programming model and implemented by specific software, which is the final arbiter as to what the pro-

gramming model is. PARKBENCH has initially adopted two such models:

- 1. Fortran77 + PVM: This is the classical distributed-memory MIMD model in which a number of separate logical processors execute asynchronously independent Fortran77 programs in their individual and separate memory space. The only communication and synchronisation between these programs is by sending messages containing data using the PVM (Parallel Virtual Machine [2]) library of Fortran communication subroutines.

- 2. High Performance Fortran (HPF): This is an extension of the classical SIMD model in which a single instruction stream in the Fortran90 language [4] specifies operations that apply, notionally simultaneously, to vectors and higher-order arrays of data. In HPF [5] data distribution statements are added by the programmer as comments to the Fortran90 program to help the compiler generate efficient code on a distributed-memory computer system.

A benchmark is therefore testing a software interface to a computer, and not a particular type of computer architecture. For example, benchmarks using the "F77+PVM" programming model can be run on any computer providing this interface, both distributed-memory message-passing computers which have message-passing hardware, and shared-memory computers which lack the hardware but can simulate message-passing in software.

## 1.5 Computer Terminology

Nevertheless, most of our benchmarks are written to the distributed-memory MIMD programming model, with so-called scalable distributed-memory hardware in mind. The hardware of such computers consists of a large number of "nodes" connected by a communication network (typically with a mesh or hypercube topology), across which messages pass between the nodes. Each node typically contains one or more microprocessors for performing arithmetic (perhaps some with vector processing capabilities), communication chips that are used to interface with the network, and local memory. For this reason, the computational parts of the computer are commonly referred to as either "nodes" or "processors", and the com-

puter is scaled up in size by increasing their number. Both names are acceptable, but "nodes" is perhaps preferable for use in descriptions of the hardware, because we can then say that one node may contain several processors.

The F77+PVM programming model that we are using is, however, much simpler, in that the node is the smallest element of the computer that can be programmed, and it is always used as if it contained a single processor, because it runs a single F77 program. If the hardware actually uses several processors to run the single program faster, this should be beneficial to the benchmark result, but it is hidden from the programmer. Thus from the programmer's view, there is no useful distinction between node and processor, and in this document we have tried to use the term "processor" consistently to mean the "logical processor" of the F77+PVM programming model. whether or not it may be implemented by one or several physical processors.

# 1.6 How to Get the PARKBENCH Report and Benchmarks

An up-to-date copy of all the PARKBENCH material is available from netlib. The index of material available may be obtained in several ways:

(1) From any machine on the Internet type:

rcp anon@netlib2.cs.utk.edu:

parkbench/index index

(2) Anonymous ftp to netlib2.cs.utk.edu

cd parkbench get index quit

(3) Sending email to netlib@ornl.gov and in the message type:

send index from parkbench

(4) Use Xnetlib and click "library", click "parkbench", click "parkbench/index", click "download", click "Get Files Now". (Xnetlib is an X-window interface to the netlib

#### 104 PARKBENCH COMMITTEE

software based on a client-server model. The software can be found in netlib.)

The required material can then be obtained with a further "get".

The latest version of this PARKBENCH report that is available for public electronic distribution can be found in the file parkbench.ps. The various benchmarks will appear as compressed and unencoded tar files as they become available. A collection of other benchmarks are also available, and the index adequately explains their content.

# Chapter 2

# Methodology\*

## 2.1 Philosophy

One might ask why anyone should care about developing a standardized, rigorous and scientifically tenable methodology for studying the performance of high-performance computer systems. There are several reasons why this is an important undertaking:

- 1. To establish and maintain high standards of honesty and integrity in our profession.

- 2. To improve the status of supercomputer performance analysis as a rigorous scientific discipline.

- 3. To reduce confusion in the high-performance computing literature.

- 4. To increase understanding of these systems, both at a low-level hardware or software level and at a high-level, total system performance level.

- To assist the purchasers of high-performance computing equipment in selecting systems best suited to their needs.

- To reduce the amount of time and resources vendors must expend in implementing multiple, redundant benchmarks.

- To provide valuable feedback to vendors on bottlenecks that can be alleviated in future products.

It is important to note that researchers in many scientific disciplines have found it necessary to establish and refine standards for performing experiments and reporting the results. Many scientists have learned the importance of standard terminology and notation. Chemists, physicists and biologists long ago discovered the importance of *controls* in their experiments. The issue of repeat-

ability proved crucial in the recent *cold fusion* episode. Medical researchers have found it necessary to perform *double-blind* experiments in their field. Psychologists and sociologists have developed highly refined experimental methodologies and advanced data analysis techniques. Political scientists have found that subtle differences in the phrasing of a question can affect the results of a poll. Researchers in many fields have found that environmental factors in their experiments can significantly influence the measured results: thus they must carefully report all such factors in their papers.

If supercomputer performance analysis and benchmarking is ever to be taken seriously as a scientific discipline, certainly its practitioners should be expected to adhere to standards that prevail in other disciplines. This document is dedicated to promoting these standards in our field.

#### 2.2 Fundamental Metrics

The conclusions drawn from a benchmark study of computer performance depend not only on the basic timing results obtained, but also on the way these are interpreted and converted into performance figures. The choice of the performance metric, may itself influence the conclusions. For example, do we want the computer that generates the most megaflop per second (or has the highest Speedup), or the computer that solves the problem in the least time? It is now well known that high values of the first metrics do not necessarily imply the second property. This confusion can be avoided by choosing a more suitable metric that reflects solution time directly, for example either the Temporal. Simulation or Benchmark performance, defined below. This issue of the sensible choice of performance metric is becoming increasingly important with the advent of massively parallel computers which have the potential of very

<sup>\*</sup> Assembled by David Bailey for methodology subcommitee.

high megaflop rates, but have much more limited potential for reducing solution time.

#### 2.3 Time Measurement

Before other issues can be considered, we must discuss the measurement of run time. In recent years a consensus has been reached among many scientists in the field that the most relevant measure of run time is actual wall-clock elapsed time. This measure of time will be required for all PARKBENCH results that are posted to the database.

Elapsed wall-clock time means the time that would be measured on an external clock that records the time-of-day or even Coordinated Universal Time (UTC), between the start and finish of the benchmark. We are not concerned with the origin of the time measurement, since we are taking a difference, but it is important that the time measured would be the same as that given by a difference between two measurements of UTC. if it were possible to make them. It is important to be clear about this, because many computer clocks (e.g., Sun Unix function ETIME) measure elapsed CPU time, which is the total time that the process or job which calls it has been executing in the CPU. Such a clock does not record time (i.e. it stops ticking) when the job is swapped out of the CPU. It does not record, therefore, any wait time which must be included if we are to assess correctly the performance of a parallel program. On some systems, scientists have found that even for programs that perform no explicit I/O, considerable system time is nonetheless involved. for example in fetching certain library routines or other data.

Only timings actually measured may be cited for PARKBENCH benchmarks (and we strongly recommend this practice for other benchmarks as well). Extrapolations and projections, for instance to a larger number of processors, may not be employed for any reason. Also, in the interests of repeatability it is highly recommended that timing runs be repeated, several times if possible.

Two low-level benchmarks are provided in the PARKBENCH suite to test the precision and accuracy of the clock that is to be used in the benchmarking. These should be run first, before any benchmark measurements are made. They are:

1. TICK1 - measures the precision of the clock by measuring the time interval between ticks

- of the clock. A clock is said to tick when it changes its value.

- 2. TICK2 measures the accuracy of the clock by comparing a given time interval measured by an external wall-clock (the benchmarker's wrist watch is adequate) with the same interval measured by the computer clock. This tests the scale factor used to convert computer clock ticks to seconds, and immediately detects if a CPU-clock is incorrectly being used.

The fundamental measurement made in any benchmark is the elapsed wall-clock time to complete some specified task. All other performance figures are derived from this basic timing measurement. The benchmark time. T(N; p), will be a function of the problem size, N, and the number of processors, p. Here, the problem size is represented by the vector variable. N. which stands for a set of parameters characterising the size of the problem: e.g., the number of mesh points in each dimension, and the number of particles in a particle-mesh simulation. Benchmark problems of different sizes can be created by multiplying all the size parameters by suitable powers of a single scale factor, thereby increasing the spatial and particle resolution in a sensible way, and reducing the size parameters to a single size factor (usually

We believe that it is most important to regard execution time and performance as a function of at least the two variables (N; p), which define a parameter plane. Much confusion has arisen in the past by attempts to treat performance as a function of a single variable. by taking a particular path through this plane, and not stating what path is taken. Many different paths may be taken, and hence many different conclusions can be drawn. It is important, therefore, always to define the path through the performance plane, or better as we do here, to study the shape of the two-dimensional performance hill. In some cases there may even be an optimum path up this hill. The following discussion of units and metrics is based on that of Hockney [6].

### 2.4 Units and Symbols

A rational set of units and symbols is essential for any numerate science including benchmarking. The following extension of the internationally agreed SI system of physical units [7] is made to accommodate the needs of computer benchmarking.

The value of a variable comprises a pure number stating the number of units which equal the value of the variable, followed by a unit symbol specifying the unit in which the variable is being measured. A new unit is required whenever a quantity of a new nature arises, such as the first appearance of vector operations, or message sends. Generally speaking a unit symbol should be as short as possible, consistent with being easily recognised and not already used. The following have been found necessary in the characterisation of computer and benchmark performance in science and engineering. No doubt more will have to be defined as benchmarking enters new areas.

New unit symbols and their meaning:

- 1. flop: floating-point operation [latex\flop]

- 2. inst: instruction of any kind [latex\inst]

- 3. intop: integer operation [latex\inop]

- 4. vecop: vector operation [latex\vecop]

- 5. send: message send operation [latex\send]

- 6. iter: iteration of loop [latex\iter]

- 7. mref: memory reference (read or write) [latex\mref]

- 8. barr: barrier operation [latex\barr]

- 9. b: binary digit (bit) [latex\bit]

- 10. B: byte (groups of 8 bits) [latex\B]

- 11. sol: solution or single execution of a benchmark [latex\sol;

- 12. w: computer word. Symbol is lower case (W means watt) [latex\w]

- 13. tstep: timestep

When required a subscript may be used to show the number of bits involved in the unit. For example: a 32-bit floating-point operation flop<sub>32</sub>, a 64-bit word  $\mathbf{w}_{64}$ , also we have  $\mathbf{b} = \mathbf{w}_1$ ,  $\mathbf{B} = \mathbf{w}_8$ ,  $\mathbf{w}_{64} = 8\mathbf{B}$ .

Note that flop. mref and other multi-letter symbols are inseparable four or five-letter symbols. The character case is significant in all unit symbols so that e.g. Flop, Mref. W<sub>0+</sub> are incorrect. Unit symbols should always be printed in roman type. to contrast with variables names which are printed in italic. To aid in the use of roman type, especially within LATEX's math mode, LATEX commands have been defined for each unit, these commands being a backslash followed by the unit symbol (except for 'intop' and 'b' whose names are changed in the command to avoid a clash with already defined system commands). Such commands will print in roman type wherever they oc-

cur. Because 's' is the SI unit for seconds, unit symbols like 'sheep' do not take 's' in the plural. Thus we count: one flop, two flop, . . ., one hundred flop etc. This is especially important when the unit symbol is used in ordinary text as a useful abbreviation. as often, quite sensibly, it is.

SI provides the standard prefixes:

- 1. k : kilo meaning 10<sup>3</sup>

- 2. M: mega meaning 106

- 3. G: giga meaning 10°

- 4. T: tera meaning  $10^{12}$

This means that we cannot use M to mean 1024<sup>2</sup> (the binary mega) as is often done in describing computer memory capacity, e.g. 256 MB. We can however introduce the new prefix:

- 1. K : meaning 1024, then use a subscript 2 to indicate the binary versions

- 2.  $M_2$ : binary mega  $1024^2$

- 3.  $G_2$ : binary giga  $1024^3$

- 4. T<sub>2</sub>: binary tera 1024<sup>+</sup>

In most cases the difference between the mega and the binary mega (4%) is probably unimportant, but it is important to be unambiguous. In this way we can continue with existing practice if the difference doesn't matter, and have an agreed method of being more exact when necessary. For example, the above memory capacity was probably intended to mean 256M<sub>2</sub>B.

As a consequence of the above, an amount of computational work involving  $\pm .5 \times 10^{12}$  floating-point operations is correctly written as  $\pm .5$  Tflop. Note that the unit symbol Tflop is never pluralised with an added 's', and it is therefore incorrect to write the above as  $\pm .5$  Tflops which could be confused with a rate per second. The most frequently used unit of performance, millions of floating-point operations per second is correctly written Mflop/s, in analogy to km/s. The slash is necessary and means 'per', because the 'p' is an integral part of the unit symbol 'flop' and cannot also be used to mean 'per'.

## 2.5 Floating-Point Operation Count

Although we discourage the use of millions of floating-point operations per second as a performance metric, it can be a useful measure if the number of floating-point operations, F(N), needed to solve the benchmark problem is carefully defined.

For simple problems (e.g. matrix multiply) it is sufficient to use a theoretical value for the floating-point operation count (in this case  $2n^3$  flop. for nxn matrices) obtained by inspection of the code or consideration of the arithmetic in the algorithm. For more complex problems containing data-dependent conditional statements, an empirical method may have to be used. The sequential version of the benchmark code defines the problem and the algorithm to be used to solve it. Counters can be inserted into this code or a hardware monitor used to count the number of floating-point operations. The latter is the procedure followed by the PERFECT Club [8]. In either case a decision has to be made regarding the number of flop that are to be credited for different types of floating-point operations, and we see no good reason to deviate from those chosen by McMahon [9] when the Mflop/s measure was originally defined. These are:

add, subtract, multiply 1 flop 4 flop divide, square-root exponential. sine etc. 8 flop (this figure will be adjusted) IF(X .REL. Y) 1 flop

Some members of the committee felt that these numbers, derived in the 1970s, no longer correctly reflected the situation on current computers. However, since these numbers are only used to calculate a nominal benchmark flopcount, it is not so important that they be accurate. The important thing is that they do not change. otherwise all previous flop-counts would have to be renormalised. In any case, it is not possible for a single set of ratios to be valid for all computers and library software. The committee agreed that above ratios should be kept for the time being, but that the value for the transcendental functions was unrealistic and would be adjusted later after research into a more realistic and higher value.

We distinguish two types of operation count. The first is the nominal benchmark floating-point operation count,  $F_B(N)$ , which is found in the above way from the defining Fortran?? sequential code. The other is the actual number of floatingpoint operations performed by the hardware when executing the distributed multi-processor version.  $F_H(N; p)$ , which may be greater than the nominal benchmark count, due to the distributed version performing redundant arithmetic operations. Because of this. the hardware flop count may also depend on the number of processors on which the benchmark is run, as shown in its argument list.

#### 2.6 Performance Metrics

Given the time of execution T(N; p) and the flopcount F(N) several different performance measures can be defined. Each metric has its own uses, and gives different information about the computer and algorithm used in the benchmark. It is important therefore to distinguish the metrics with different names, symbols and units, and to understand clearly the difference between them. Much confusion and wasted work can arise from optimising a benchmark with respect to an inappropriate metric. The principal performance metrics are discussed in the following subsections.

## 2.6.1 Temporal Performance

If we are interested in comparing the performance of different algorithms for the solution of the same problem, then the correct performance metric to use is the Temporal Performance.  $R_T$ , which is defined as the inverse of the execution time

$$R_T(N; \rho) = T^{-1}(N; \rho)$$

(2.1)

The units of temporal performance are. in general, solutions per second (sol/s), or some more appropriate absolute unit such as timesteps per second (tstep/s). With this metric we can be sure that the algorithm with the highest performance executes in the least time, and is therefore the best algorithm. We note that the number of flop does not appear in this definition. because the objective of algorithm design is not to perform the most arithmetic per second. but rather it is to solve a given problem in the least time, regardless of the amount of arithmetic involved. For this reason the temporal performance is also the metric that computer users should employ to select the best algorithm to solve their problems, because their objective is also to solve the problem in the least time. and they do not care how much arithmetic is done to achieve this.

#### 2.6.2 Simulation Performance

A special case of temporal performance occurs for simulation programs in which the benchmark problem is defined as the simulation of a certain period of physical time, rather than a certain number of timesteps. In this case we speak of the Simulation Performance and use units such as

simulated days per day (written sim-d/d or 'd'/d) in weather forecasting, where the apostrophe is used to indicate 'simulated'; or simulated picoseconds per second (written simps/s or 'ps'/s) in electronic device simulation. It is important to use simulation performance rather than timestep/s if we are comparing different simulation algorithms which may require different sizes of timestep for the same accuracy (for example an implicit scheme that can use a large timestep, compared with an explicit scheme that requires a much smaller step). In order to maintain numerical stability, explicit schemes also require the use of a smaller timestep as the spatial grid is made finer. For such schemes the simulation performance falls off dramatically as the problem size is increased by introducing more mesh points in order to refine the spatial resolution: the doubling of the number of mesh-points in each of three dimensions can reduce the simulation performance by a factor near 16 because the timestep must also be approximately halved. Even though the larger problem will generate more Megaflop per second. in forecasting, it is the simulated days per day (i.e. the simulation performance) and not the Mflop/s. that matter to the user.

As we see below, benchmark performance is also measured in terms of the amount of arithmetic performed per second or Mflop/s. However it is important to realise that it is incorrect to compare the Mflop/s achieved by two algorithms and to conclude that the algorithm with the highest Mflop/s rating is the best algorithm. This is because the two algorithms may be performing quite different amounts of arithmetic during the solution of the same problem. The temporal performance metric.  $R_T$ . defined above, has been introduced to overcome this problem, and provide a measure that can be used to compare different algorithms for solving the same problem. However, it should be remembered that the temporal performance only has the same meaning within the confines of a fixed problem, and no meaning can be attached to a comparison of the temporal performance on one problem with the temporal performance on another.

#### 2.6.3 Benchmark Performance

In order to compare the performance of a computer on one benchmark with its performance on another, account must be taken of the different amounts of work (measured in flop) that the different problems require for their solution. Using

the flop-count for the benchmark,  $F_B(N)$ , we can define the *Benchmark Performance* as

$$R_B(N; p) = F_B(N)/T(N; p)$$

(2.2)

The units of benchmark performance are Mflop/s (benchmark name), where we include the name of the benchmark in parentheses to emphasise that the performance may depend strongly on the problem being solved, and to emphasise that the values are based on the nominal benchmark flopcount. In other contexts such performance figures would probably be quoted as examples of the socalled sustained performance of a computer. We feel that the use of this term is meaningless unless the problem being solved and the degree of code optimisation is quoted. because the performance is so varied across different benchmarks and different levels of optimisation. Hence we favour the quotation of a selection of benchmark performance figures, rather than a single sustained performance, because the latter implies that the quoted performance is maintained over all prob-

Note also that the flop-count  $F_B(N)$  is that for the defining sequential version of the benchmark. and that the same count is used to calculate  $R_B$  for the distributed-memory (DM) version of the program, even though the DM version may actually perform a different number of operations. It is usual for DM programs to perform more arithmetic than the defining sequential version, because often numbers are recomputed on each processor in order to save communicating their values from a master processor. However such calculations are redundant (they have already been performed on the master) and it would be incorrect to credit them to the flop-count of the distributed program.

Using the sequential flop-count in the calculation of the DM programs benchmark performance has the additional advantage that it is possible to conclude that, for a given benchmark, the implementation that has the highest benchmark performance is the best because it executes in the least time. This would not necessarily be the case if a different  $F_B(N)$  were used for different implementations of the benchmark. For example, the use of a better algorithm which obtains the solution with less than  $F_B(N)$  operations will show up as higher benchmark performance. For this reason it should cause no surprise if the benchmark performance occasionally exceeds the maximum possible hardware performance. To this extent benchmark performance Mflop/s must be understood to be nominal values, and not necessarily exactly the number of operations executed per second by the hardware, which is the subject of the next metric. The purpose of benchmark performance is to compare different implementations and algorithms on different computers for the solution of the same problem, on the basis that the best performance means the least execution time. For this to be true  $F_B(N)$  must be kept the same for all implementations and algorithms.

#### 2.6.4 Hardware Performance

If we wish to compare the observed performance with the theoretical capabilities of the computer hardware, we must compute the actual number of floating-point operations performed,  $F_H(N; \rho)$ , and from it the actual  $Hardware\ Performance$

$$R_H(N; p) = F_H(N; p) / T(N; p)$$

(2.3)

The hardware performance also has the units Mflop/s. and will have the same value as the benchmark performance for the sequential version of the benchmark. However, the hardware performance may be higher than the benchmark performance for the distributed version, because the hardware performance gives credit for redundant arithmetic operations, whereas the benchmark performance does not. Because the hardperformance measures the floating-point operations performed per second. unlike the benchmark performance, it can never exceed the theoretical peak performance of the computer.

Assuming a computer with multiple-CPUs each with multiple arithmetic pipelines, delivering a maximum of one flop per clock period, the theoretical peak value of hardware performance is

$$r^* = \frac{fl.pt.pipes/CPU}{clock.period} \times number.CPUs \quad (2.4)$$

with units of Mflop/s if the clock period is expressed in microseconds. By comparing the measure hardware performance,  $R_H(N; p)$ , with the theoretical peak performance, we can assess the fraction of the available performance that is being realised by a particular implementation of the benchmark.

# 2.6.5 Speedup, Efficiency and Performance per Node

Parallel speedup is a popular metric that has been used for many years in the study of parallel com-

puter performance. However, its definition is open to ambiguity and misuse because it always begs the question "speedup over what?"

Speedup is usually defined as

$$\frac{T_1}{T_\rho} \tag{2.5}$$

where  $T_{\rho}$  is the  $\rho$ -processor time to perform some benchmark, and  $T_1$  is the one-processor time. There is no doubt about the meaning of  $T_p$ —this is the measured time T(N; p) to perform the benchmark. There is often considerable dispute over the meaning of  $T_1$ : should it be the time for the parallel code running on one processor, which probably contains unnecessary parallel overhead. or should it be the best serial code (possibly using a different algorithm) running on one processor? Many scientists feel the latter is a more responsible choice, but this requires research to determine the best practical serial algorithm for the given application. If at a later time a better algorithm is found, current speedup figures might be considered obsolete. An additional difficulty with this definition is that even if a meaning for  $T_1$  is agreed to, there may be insufficient memory on a single processor to store an entire large problem. Thus in many cases it may be impossible to measure  $T_1$ using this definition.

One principal objective in the field of performance analysis is to compare the performance of different computers by benchmarking. It is generally agreed that the best performance corresponds to the least wall-clock execution time. In order to adapt the speedup statistic for benchmarking, it is thus necessary to define a single reference value of  $T_1$  to be used for all calculations. It does not matter how  $T_1$  is defined, or what its value is, only that the same value of  $T_1$  is used to calculate all speedup values used in the comparison.

However, defining  $T_1$  as a reference time unrelated to the parallel computer being benchmarked unfortunately has the consequence that many properties that many people regard as essential to the concept of parallel speedup are lost:

- 1. It is no longer necessarily true that the speedup of the parallel code on one processor is unity. It may be, but only by chance.

- 2. It is no longer true that the maximum speedup using p-processors is p.

- 3. Because of the last item, efficiency figures computed as speedup divided by *p* are no longer a meaningful measure of processor utilization.

There are other difficulties with this formulation of speedup. If we use  $T_1$  as the run time on a very fast single processor (currently, say, a Cray C90 or a NEC SX-3), then manufacturers of highly parallel systems will be reluctant to quote the speedup of their system in the above way. For example, if the speedup of a 100 processor parallel system over a single processor of the same system is a respectable factor of 80, it is likely that the speedup computed from the *standard*  $T_1$  would be reduced to 10 or less. This is because a fast vector processor is typically at least ten times faster than the RISC processors used in many highly parallel systems of a comparable generation.

Thus it appears that if we sharpen the definition of speedup to make it an acceptable metric for comparing the performance of different computers. we have to throw away the main properties that have made the concept of speedup useful in the past.

Accordingly, the PARKBENCH committee has decided the following:

- 1. No speedup statistic will be kept in the PARKBENCH database.

- Speedup statistics based on PARKBENCH benchmarks must never be used as figures of merit when comparing the performance of different systems. We further recommend that speedup figures based on other benchmarks not be used as figures of merit in such comparisons.

- Speedup statistics may be used in a study of the performance characteristics of an individual parallel system. But the basis for the determination of T<sub>1</sub> must be clearly and explicitly stated.

- 4. The value of T<sub>1</sub> should be based on an efficient uniprocessor implementation. Code for message passing, synchronization, etc. should not be present. The author should also make a reasonable effort to insure that the algorithm used in the uniprocessor implementation is the best practical serial algorithm for this purpose.

- 5. Given that a large problem frequently does not fit on a single processor, it is permissible to cite speedup statistics based on the timing of a smaller number of processors. In other words, it is permissible to compute speedup as  $T_p/T_m$ , for some m,  $1 \le m \le p$ . If this is done, however, this usage must be clearly stated, and full details of the basis of this calculation must be presented. As

above, care must be taken to insure that the unit timing  $T_m$  is based on an efficient implementation of appropriate algorithms.

#### 2.7 Performance Database

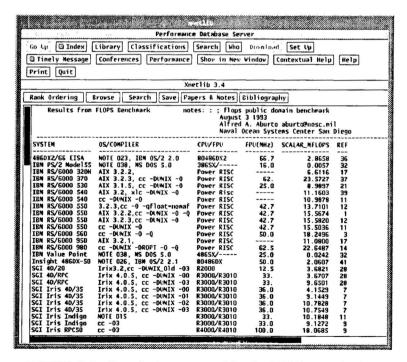

The process of gathering, archiving, and distributing computer benchmark data is a cumbersome task usually performed by computer users and vendors with little coordination. Within Xnetlib [10] there is a mechanism to provide Internet-access to a performance database server (PDS) which can be used to extract current benchmark data and literature. PDS [11] provides an on-line catalog of public-domain computer benchmarks such as the LINPACK Benchmark [12], Perfect Benchmarks [8]. and the NAS Parallel Benchmarks [13]. PDS does not reformat or present the benchmark data in any way that conflicts with the original methodology of any particular benchmark; it is thereby devoid of any subjective interpretations of machine performance. PDS is providing a more manageable approach to the development and support of a large dynamic database of published performance metrics.

The PDS system was developed at the University of Tennessee and Oak Ridge National Laboratory and is an initial attempt at performance data management. This on-line database of computer benchmarks is specifically designed to provide easy maintenance, data security, and data integrity in the benchmark information contained in a *dynamic* performance database.

PDS was designed with a simple tabular format that involves displaying the data in rows (machine configuration) and columns (numbers). Graphical representations of tabular data, such as the representation by SPEC [14] with the obsolescent SPECmarks, are straightforward.

## 2.7.1 Design of a Performance Database

Because of the complexity and volume of the data involved in a performance database, it is natural to exploit a database management system (DBMS) to archive and retrieve benchmark data. A DBMS will help not only in managing the data, but also in assuring that the various benchmarks are presented in some reasonable format for users: table or spreadsheet where machines are *rows* and benchmarks are *columns*.

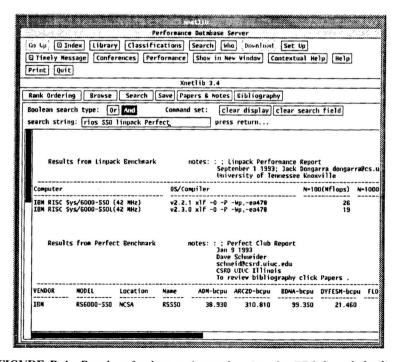

Of major concern is the organization of the data. It seems logical to organize data in the DBMS according to the benchmarks themselves: a

LINPACK table, a Perfect table, etc. It would be nearly impossible to *force* these very different presentation formats to conform to a single presentation standard just for the sake of reporting. Individual tables preserve the display characteristics of each benchmark, but the DBMS should allow users to query all tables for various machines. Parsing benchmark data into these tables is straightforward provided a customized parser is available for each benchmark set. In the parsing process, constructing a raw data file and building a standard format ASCII file eases the incorporation of the data into the database.

The functionality required by PDS is not very different from that of a standard database application. The difference lies in the user interface. Financial databases, for example, typically involve specific queries like

#### EXTRACT ROW ACCT\_NO = R103049

in which data points are usually discrete and the user is very familiar with the data. The user, in this case, knows exactly what account number to extract, and the format of retrieved data in response to queries. With our performance database, however, we would expect the contrary: the user does not really know (i) what kind of data is available. (ii) how to request/extract the data, and (iii) what form to expect the returned data to be in. These assumptions are based on the current lack of coordination in (public-domain) benchmark management. The number of benchmarks in use continues to rise with no standard format for presenting them. The number of performanceliterate users is increasing, but not at a rate sufficient to expect proper queries from the performance database. Quite often, users just wish to see the best-performing machines for a particular benchmark. Hence, a simple rank-ordering of the rows of machines according to a specific benchmark column may be sufficient for a general user.

Finally, the features of the PDS user interface should include

- (1) the ability to extract specific machine and benchmark combinations that are of interest.

- (2) the ability to search on multiple keywords across the entire dataset, and

- (3) the ability to view cross-referenced papers and bibliographic information about the benchmark itself.

We include (3) in the list above to address the concern of proliferating numbers without any benchmark methodology information. PDS would provide abstracts and complete papers related to benchmarks and thereby provide a needed educational resource without risking improper interpretation of retrieved benchmark data.

#### 2.7.2 PDS Features

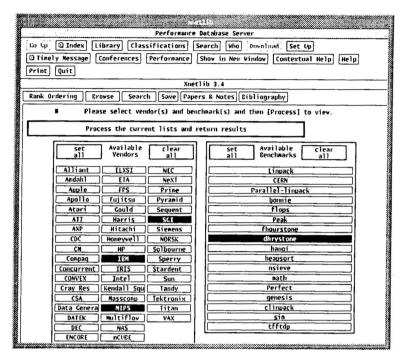

PDS provides the following retrieval-based functions for the user:

- (1) a *browse* feature to allow casual viewing and point-and-click navigation through the database.

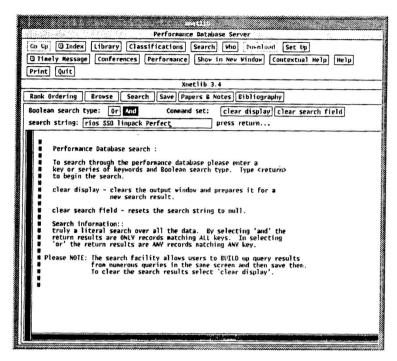

- (2) a search feature to permit multiple keyword searches with Boolean conditions.

- (3) a rank-ordering feature to sort and display the results for the user, and

- (4) a few additional features that aid the user in acquiring benchmark documentation and references.

As discussed in [11], the Rank Ordering option in PDS allows the user to view a listing of machines that have been ranked by a particular performance metric such as megaflop/s or elapsed CPU time. Both Rank Ordering and Papers options are menu-driven data access paths within PDS. With the Browse facility in PDS, the user first selects the vendor(s) and benchmark(s) of interest, then selects the large Process button to query the performance database. The PDS client then opens a socket connection to the server and, using the query language (rdb), remotely queries the database. The Search option in PDS permits user-specified keyword searches over the entire performance database. Search utilizes literal case-insensitive matching along with a moderate amount of aliasing. Multiple keywords are permitted, and a Boolean flag is provided for more complicated searches. Using Search, the user has the option of entering vendor names, machine aliases, benchmark names. or specific strings, or producing a more complicated Boolean keyword search. Since any retrieved data will be displayed to the screen (by default), the Save option allows the user to store any retrieved performance data to an ASCII file. Finally, the Bibliography option in PDS provides a list of relevant manuscripts and other information about the benchmarks. Future enhancements to PDS include the use of more

sophisticated two-dimensional graphical displays for machine comparisons. Additional serial and parallel benchmarks will be added to the database as formal procedures for data acquisition are determined. The Browse and Search facilities available in the current version of PDS are illustrated in Appendix B.

### 2.7.3 PDS Availability

To receive Xnetlib with PDS support for Unix-based machines, send the electronic mail message send xnetlib.shar from xnetlib to netlib @ornl.gov. You can unshar the file and compile it by answering the user-prompted questions upon installation. Use of shar will install the full functionality of Xnetlib along with the latest PDS client tool. Questions concerning PDS should be sent to utpds@cs.utk.edu. The University of Tennessee and Oak Ridge National Laboratory will be responsible for gathering and archiving additional (published) benchmark data.

At present each benchmark measurement for a particular problem size N and processor number  $\rho$ , is represented by one line in the database with variable length fields chosen by the benchmark writer as suitable and comprehensive to describe the conditions of the benchmark run. The fields separated by a marker include, benchmarker's name and e-mail, computer location and date, hardware specification, compiler data and optimisation level, N,  $\rho$ ,  $T(N; \rho)$ ,  $R_B(N; P)$  and other metrics as deemed appropriate by the benchmark writer. Ideally, the line for the database would be produced automatically as output by the benchmark program itself.

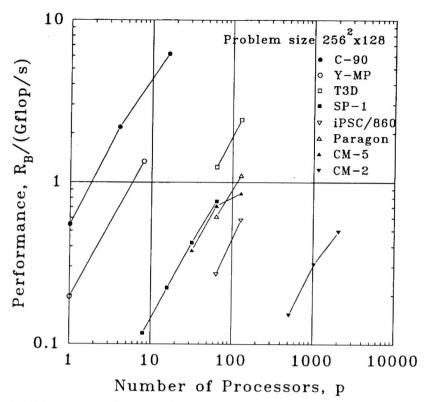

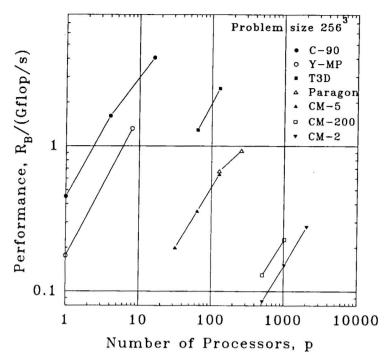

#### 2.8 Interactive Graphical Interface

The Southampton Group has agreed to provide an interactive graphical front end to the PARKBENCH PDS database of performance results. To achieve this, the basic data held in the Performance Data Base should be values of T(N; p) for at least 4 values of problem size N, each for sufficient p-values (say 5 to 10) to determine the trend of variation of performance with number of processors for constant problem size. It is important that there be enough p-values to see any saturation in performance, if present, or any peak in performance followed by degradation. A graphical interface is really essential to allow this multidimensional data to be viewed in any of the metrics defined above, as chosen interactively by

the user. The user could also be offered (by suitable interpolation) a display of the results in various scaled metrics, in which the problem size is expanded with the number of processors.

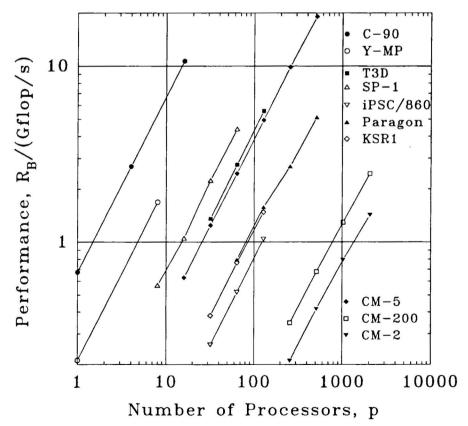

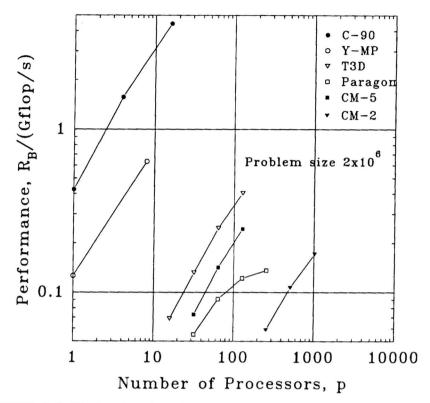

In order to encompass as wide a range of performance and number of processors as possible, a log-scale on both axes is unavoidable, and the format and scale range should be kept fixed as long as possible to enable easy comparison between graphs. A three-cycle by three-cycle log/log graph with range 1 to 1000 in both p and Mflop/s would cover most needs in the immediate future. Examples of such graphs are to be found in [6, 15].

A log/log graph is also desirable because the size and shape of the Amdahl saturation curve is the same wherever it is plotted on such a graph. i.e. there is a universal Amdahl curve that is invariant to its position on any  $\log/\log$  graph. Amdahl saturation is a two-parameter description of any of the performance metrics, R, as a function of p for fixed N, which can be expressed by

$$R = \frac{R_{\infty}}{(1 + \rho_{\frac{1}{2}}/\rho)} \tag{2.6}$$

where  $R_{\infty}$  is the saturation performance approached as  $p \to \infty$  and  $p_{\frac{1}{2}}$  is the number of processors required to reach half the saturation performance. The graphical interface should allow this universal Amdahl curve to be moved around the graphical display, and be matched against the performance curves. The changing values of the two parameters  $(R_{\infty}, p_{\frac{1}{2}})$  should be displayed as the Amdahl curve is moved.

As more experience is gained with performance analysis, that is the fitting of performance data to parameterised formulae, it is to be expected that the graphical interface will allow more complicated formulae to be compared with the experimental data, perhaps allowing 3 to 5 parameters in the theoretical formula. But, as yet, we do not know what these parameterised formula should be.

# 2.9 Benchmarking Procedure and Code Optimisation

Manufacturers will always feel that any benchmark not tuned specifically by themselves, is an unfair test of their hardware and software. This is inevitable and from their viewpoint it is true. NASA have overcome this problem by only specifying the problems (the NAS paper-and-pencil

benchmarks [16]) and leaving the manufacturers to write the code, but in many circumstances this would require unjustifiable effort and take too long. It is also a perfectly valid question to ask how a particular parallel computer will perform on existing parallel code, and that is the viewpoint of PARKBENCH.

The benchmarking procedure is to run the distributed PARKBENCH suite on an as-is basis. making only such non-substantive changes that are required to make the code run (e.g. changing the names of header files to a local variant). The as-is run may use the highest level of automatic compiler optimisation that works, but the level used and compiler date should be noted in the appropriate section of the performance database entry.

After completing the as-is run, which gives a base-line result, any form of optimisation may be applied to show the particular computer to its best advantage, up to completely rethinking the algorithm, and rewriting the code. The only requirement on the benchmarker is to state what has been done. However, remember that, even if the algorithm is changed, the official flop-count,  $F_B(N)$  that is used in the calculation of nominal

benchmark Mflop/s,  $R_B(N; p)$ , does not. In this way a better algorithm will show up with a higher  $R_B$ , as we would want it to, even though the hardware Mflop/s is likely to be little changed.

Typical steps in optimisation might be:

- 1. explore the effect of different compiler optimisations on a single processor, and choose the best for the as-is run.

- 2. perform the as-is run on multiple processors, using enough values of *p* to determine any peak in performance or saturation.

- 3. return to single processor and otpimise code for vectorisation, if a vector processor is being used. This means restructuring loops to permit vectorisation.

- 4. continue by replacement of selected loops with optimal assembly coded library routines (e.g. BLAS [17] where appropriate).

- 5. replacement of whole benchmark by a tuned library routine with the same functionality.

- 6. replace the whole benchmark with a locally written version with the same functionality but using possibly an entirely different algorithm that is more suited to the architecture.

## Chapter 3

## Low-Level Benchmarks\*

#### 3.1 Introduction

The first step in the assessment of the performance of a parallel computer system is to measure the performance of a single logical processor of the multi-processor system. There exist already many good and well-established benchmarks for this purpose, notably the LINPACK benchmarks and the Livermore Loops. These are not part of the PARKBENCH suite of programs, but PARKBENCH recommends that these be used to measure single-processor performance, in addition to some specific low-level measurements of its own (see Section 3.2). There follows a brief description of existing benchmarks that are recommended for measuring single-processor performance, with a discussion of their value.

# 3.1.1 Most Reported Benchmark: LINPACKD (n = 100)

This well-known standard benchmark is a Fortran program for the solution of  $(100 \times 100)$  dense set of linear equations by Gaussian elimination. It is distributed by Jack Dongarra of the University of Tennessee [12]. The results are quoted in Mflop/s and are regularly published and available by electronic mail. The main value of this benchmark is that results are known for more computers than any other benchmark. Most of the compute time is contained in vectorisable DO-loops such as the DAXPY (scalar times vector plus vector) and inner product. Therefore one expects vector computers to perform well on this benchmark. The weakness of the benchmark is that it tests only a small number of vector operations, but it does include the effect of memory access and it is solving a complete (although small) real problem.

# 3.1.2 Performance Range: The Livermore Loops

These are a set of 24 Fortran DO-loops (The Livermore Fortran Kernels, LFK) extracted from operational codes used at the Lawrence Livermore National Laboratory [9]. They have been used since the early seventies to assess the arithmetic performance of computers and their compilers. They are a mixture of vectorisable and non-vectorisable loops and test rather fully the computational capabilities of the hardware. and the skill of the software in compiling efficient code, and in vectorisation. The main value of the benchmark is the range of performance that it demonstrates, and in this respect it complements the limited range of loops tested in the LINPACK benchmark. The benchmark provides the individual performance of each loop, together with various averages (arithmetic. geometric. harmonic) and the quartiles of the distribution. However, it is difficult to give a clear meaning to these averages. and the value of the benchmark is more in the distribution itself. In particular, the maximum and minimum give the range of likely performance in full applications. The ratio of maximum to minimum performance has been called the instability or the speciality [18], and is a measure of how difficult it is to obtain good performance from the computer, and therefore how specialised it is. The minimum or worst performance obtained on these loops is of special value, because there is much truth in the saying that "the best computer to choose is that with the best worst-performance."

### 3.2 Single-Processor Benchmarks

The single-processor low-level benchmarks provided by PARKBENCH, aim to measure performance parameters that characterise the basic architecture of the computer, and the compiler

<sup>\*</sup> Assembled by Roger Hockney for Low-Level subcommittee.

software through which it is used. For this reason, such benchmarks have also been called appropriately basic architectural benchmarks. Following the methodology of Euroben [19], the aim is that these hardware/compiler parameters will be used in performance formulae that predict the timing and performance of the more complex kernels (see Chapter 4) and compact applications (see Chapter 5). They are therefore a set of synthetic benchmarks contrived to measure theoretical parameters that describe the severity of some overhead or potential bottleneck, or the properties of some item of hardware. Thus RINF1 characterises the basic properties of the arithmetic pipelines by measuring the parameters  $(r_x, n_t)$  (see section 3.2.3), and POLY1 and POLY2 characterise the severity of the memory bottleneck by measuring the parameters  $(\hat{r}_{\infty}, f_{4})$  (see section 3.2.4).

The fundamental measurement in any benchmarking is the measurement of elapsed wall-clock time. Because the computer clocks on each processor of a multi-processor parallel computer are not synchronised, all benchmark time measurements must be made with a single clock on one processor of the system. The benchmarks TICK1 and TICK2 have, respectively, been designed to measure the resolution and to check the absolute value of this clock. These benchmarks should be run with satisfactory results before any further benchmark measurements are made.

#### 3.2.1 Timer Resolution: TICK1

TICK1 measures the resolution of the clock being used in the benchmark measurements, which is the time interval between successive ticks of the clock. A succession of calls to the timer routine are inserted in a loop and executed many times. The differences between successive values given by the timer are then examined. If the changes in the clock value (or ticks) occur less frequently than the time taken to enter and leave the timer routine. then most of these differences will be zero. When a tick takes place, however, a difference equal to the tick value will be recorded, surrounded by many zero differences. This is the case with clocks of poor resolution: for example most UNIX clocks that tick typically every 10 ms. Such poor UNIX clocks can still be used for low-level benchmark measurements if the benchmark is repeated, say, 10.000 times, and the timer calls are made outside this repeat loop.

With some computers, such as the CRAY series, the clock ticks every cycle of the computer,

that is to say every 6ns on the Y-MP. The resolution of the CRAY clock is therefore approximately one million times better than a UNIX clock, and that is quite a difference! If TICK1 is used on such a computer the difference between successive values of the timer is a very accurate measure of how long it takes to execute the instructions of the timer routine, and therefore is never zero. TICK1 takes the minimum of all such differences, and all it is possible to say is that the clock tick is less than or equal to this value. Typically this minimum will be several hundreds of clock ticks. With a clock ticking every computer cycle, we can make lowlevel benchmark measurements without a repeat loop. Such measurements can even by made on a busy timeshared system (where many users are contending for memory access) by taking the minimum time recorded from a sample of, sav. 10,000 single execution measurements. In this case, the minimum can usually be said to apply to a case when there was no memory access delay caused by other users.

TICK1 exists and forms part of the Genesis benchmarks [20].

#### 3.2.2 Timer Value: TICK2

TICK2 confirms that the absolute values returned by the computer clock are correct, by comparing its measurement of a given time interval with that of an external wall-clock (actually the benchmarker's wristwatch). Parallel benchmark performance can only be measured using the elapsed wall-clock time, because the objective of parallel execution is to reduce this time. Measurements made with a CPU-timer (which only records time when its job is executing in the CPU are clearly incorrect, because the clock does not record waiting time when the job is out of the CPU, TICK2 will immediately detect the incorrect use of a CPU-time-for-this-job-only clock. An example of a timer that claims to measure elapsed time but is actually a CPU-timer, is the returned value of the popular Sun UNIX timer ETIME, TICK2 also checks that the correct multiplier is being used in the computer system software to convert clock ticks to true seconds.

TICK2 exists and forms part of release 2.2 and later of the Genesis benchmarks [21].

## 3.2.3 Basic Arithmetic Operations: RINF1

This benchmark takes a set of common Fortran DO-loops and analyses their time of execution in terms of the two parameters  $(r_x, n_{\frac{1}{2}})$  [22, 23, 24.

25, 26, 27].  $r_x$  is the asymptotic performance rate in Mflop/s which is approached as the loop (or vector) length, n, becomes longer.  $n_{\frac{1}{2}}$  (the half-performance length) expresses how rapidly, in terms increasing vector length, the actual performance, r, approaches  $r_x$ . It is defined as the vector length required to achieve a performance of one half of  $r_x$ . This means that the time, t, for a DO-loop corresponding to q vector operations (i.e. with q floating-point operations per element per iteration) is approximated by

$$t = q * (n + n_{i})/r_{x}. \tag{3.1}$$

Then the performance rate is given by

$$r = \frac{q * n}{t} = \frac{r_{x}}{(1 + n_{4}/n)}.$$

(3.2)

We can see from Eqn. (3.1) that  $n_{\frac{1}{2}}$  is a way of measuring the importance of vector startup overhead  $(=n_{\frac{1}{2}}/r_{\infty})$  in terms of quantities known to the programmer (loop or vector length). In the benchmark program, the two parameters are determined by a least-squares fit of the data to the straight line defined by Eqn. (3.1). A useful guide to the significance of  $n_4$  is to note from Eqn. (3.2) that 80 percent of the asymptotic performance is achieved for vectors of length  $4 \times n_4$ . Generally speaking.  $n_k$  values of up to about 50 are tolerable, whereas the performance of computers with larger values of  $n_i$  is severely constrained by the need to keep vector lengths significantly longer than  $n_k$ . This requirement makes computers difficult to program efficiently, and often leads to disappointing performance, compared to the asymptotic rate advertised by the manufacturer.

RINF1 has been used extensively for about ten years as part of the Hockney and EuroBen benchmarks (module MOD1AC) [28]. It is also included in the Genesis benchmarks [15].

# 3.2.4 Memory-Bottleneck Benchmarks: POLY1 and POLY2

Even if the vector lengths are long enough to overcome the vector startup overhead, the peak rate of the arithmetic pipelines may not be realised because of the delays associated with obtaining data from the cache or main memory of the computer. The POLY1 and POLY2 benchmarks quantify this dependence of computer performance on memory access bottlenecks. The computational intensity, f. of a DO-loop is defined as the number of floating-point operations performed per memory reference to an element of a vector variable [27]. The asymptotic performance,  $r_{\infty}$ , of a computer is observed to increase as the computational intensity increases, because as this becomes larger, the effects of memory access delays become negligible compared to the time spent on arithmetic. This effect is characterised by the two parameters  $(\hat{r}_{\infty}, f_{\dagger})$ , where  $\hat{r}_{\infty}$  is the peak hardware performance of the arithmetic pipeline, and  $f_{\dagger}$  is the computational intensity required to achieve half this rate. That is to say the asymptotic performance is given by:

$$r_{\infty} = \frac{\hat{r}_{\infty}}{(1 + f_{\perp}/f)} \tag{3.3}$$

If memory access and arithmetic are not overlapped, then f, can be shown to be the ratio of arithmetic speed (in Mflop/s) to memory access speed (in Mw/s) [27]. The parameter  $f_i$ , like  $n_i$ , measures an unwanted overhead and should be as small as possible. In order to vary f and allow the peak performance to be approached, we choose a kernel loop that can be computed with maximum efficiency on any hardware. This is the evaluation of a polynomial by Horner's rule, in which case the computational intensity is the order of the polynomial, and both the multiply and add pipelines can be used in parallel. To measure  $f_{i}$ , the order of the polynomial is increased from one to ten, and the measured performance for long vectors is fitted to Eqn. (3.3).

The POLY1 benchmark repeats the polynomial evaluation for each order typically 1000 times for vector lengths up to 10,000, which would normally fit into the cache of a cache-based processor. Except for the first evaluation, the data will therefore be found in the cache. POLY1 is therefore an *in-cache* test of the memory bottleneck between the arithmetic registers of the processor and its cache.

POLY2, on the other hand, flushes the cache prior to each different order and then performs only one polynomial evaluation, for vector lengths from 10,000 up to 100,000, which would normally exceed the cache size. Data will have to be brought from off-chip memory, and POLY2 is an out-of-cache test of the memory bottleneck between off-chip memory and the arithmetic registers.

The POLY1 benchmark exists as MOD1G of the EuroBen benchmarks [28]. POLY2 exists as part of the Hockney benchmarks.

#### 3.3 Multi-Processor Benchmarks

The PARKBENCH suite of benchmark programs provides low-level benchmarks to characterise the basic communication properties of a parallel computer by measuring the parameters  $(r_{\infty}, n_{\dagger})$  for communication (COMMS1, COMMS2, COMMS3). The ratio of arithmetic speed to communication speed (the hardware + compiler parameter  $f_{ij}$  for communication) is measured by the POLY3 benchmark. The ability to synchronise all the processors in a parallel computer in an acceptable time, is a key requirement of such computers. The SYNCH1 benchmark assesses this by measuring the number of barrier synchronisation statements that can be executed per second as a function of the number of processors taking part in the barrier.

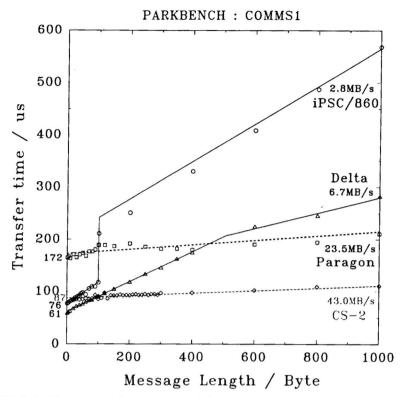

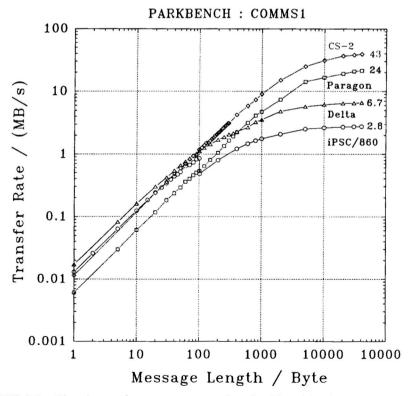

# 3.3.1 Communication Benchmarks: COMMS1 and COMMS2

The purpose of the COMMS1. or Pingpong. benchmark [18, 29] is to measure the basic communication properties of a message-passing computer. A message of variable length. n. is sent from a master processor to a slave processor. The slave receives the message into a Fortran data array, and immediately returns it to the master. Half the time for this message pingpong is recorded as the time. t, to send a message of length. n. In the COMMS2 benchmark there is a message exchange in which two processors simultaneously send messages to each other and return them. In this case advantage can be taken of bidirectional links, and a greater bandwidth can be obtained than is possible with COMMS1. In both benchmarks, the time as a function of message length is fitted by least squares using the parameters  $(r_x, n_t)$ [24, 27] to the following linear timing model:

$$t = (n + n_{\frac{1}{2}})/r_{\infty} \tag{3.4}$$

when the communication rate is given by

$$r = \frac{r_x}{1 + n_i/n} = r_x \operatorname{pipe}(n/n_i)$$

(3.5)

where

$$pipe(x) = \frac{1}{1 + 1/x}$$

(3.6)

and the startup time is

$$t_0 = n_{\rm i}/r_{\rm x} \tag{3.7}$$

In the above equations,  $r_{x}$  is the asymptotic bandwidth of communication which is approached as the message length tends to infinity (hence the subscript), and  $n_{t}$  is the message length required to achieve half this asymptotic rate. Hence  $n_{t}$  is called the half-performance message length.

The importance of the parameter  $n_4$  is that it provides a yardstick with which to measure message-length, and thereby enables one to distinguish the two regimes of short and long messages. For long messages  $(n > n_4)$ , the denominator in equation (3.5) is approximately unity and the communication rate is approximately constant at its asymptotic rate,  $r_{\infty}$

$$r \approx r_{x}$$

(3.8)

For short messages  $(n < n_i)$ , the communication rate is best expressed in the algebraically equivalent form

$$r = \frac{\pi_0 n}{(1 + n/n_4)} \tag{3.9}$$

where

$$\pi_0 = t_0^{-1} = r_x / n_{\frac{1}{2}} \tag{3.10}$$

For short messages, the denominator in equation 3.9 is approximately unity, so that

$$r \approx \pi_0 n = n/t_0 \tag{3.11}$$

In sharp contrast to the approximately constant rate in the long-message limit, the communication rate in the short message limit is seen to be approximately proportional to the message length. The constant of proportionality.  $\pi_0$ , is known as the *specific performance*, and can be expressed conveniently in units of kilobyte per second per byte (kB/s)/B or 'k/s'. Unfortunately since an SI prefix, such as k, cannot stand alone without a unit symbol, this unit must be written either as  $10^3/\text{s}$  or as kHz, where Hz is a special unit name for per second  $(s^{-1})$ .

Thus, in general, we may say that  $r_x$  characterises the long-message performance and  $\pi_0$  the short-message performance. The COMMS1 benchmark computes all four of the above parameters,  $(r_x, n_1, t_0, \text{ and } \pi_0)$ , because each emphasises a different aspect of performance. However only two of them are independent. In the case that there are different modes of transmission for messages shorter or longer than a certain length, the benchmark can read in this breakpoint and perform a separate least-squares fit for the two regions. An example is the Intel iPSC/860 which

has a different message protocol for messages shorter than and longer than 100 byte.

Because of the finite (and often large) value of t<sub>0</sub>, the above is a two-parameter description of communication performance. It is therefore incorrect. and sometimes positively misleading, to quote only one of the parameters (e.g. just  $r_x$ , as is often done) to describe the performance. The most useful pairs of parameters are  $(r_{\infty}, n_{\delta})$ .  $(\pi_0, \dots, \pi_0)$  $n_{i}$ ) and  $(t_{0}, r_{\infty})$ , depending on whether one is concerned with long vectors, short vectors or a direct comparison with hardware times. Note also that. although  $n_i$  is defined as the message length required to obtain half the asymptotic rate  $r_{\infty}$ , the two parameters  $(r_{\infty}, n_{\parallel})$  are sufficient to calculate the communication rate for any message length via equation 3.5. or equivalently using  $\pi_0$  instead of  $r_{\infty}$  via 3.9.

The COMMS1 and COMMS2 benchmarks exist as part of the Genesis benchmarks [30].

# 3.3.2 Total Saturation Bandwidth: COMMS3

To complement the above communication benchmarks, there is a need for a benchmark to measure the total saturation bandwidth of the complete communication system, and to see how this scales with the number of processors. A natural generalisation of the COMMS2 benchmark is made as follows, and called the COMMS3 benchmark: Each processor of a p-processor system sends a message of length n to the other (p-1) processors. Each processor then waits to receive the (p-1) messages directed at it. The timing of this generalised *pingpong* ends when all messages

have been successfully received by all processors, although the process will be repeated many times to obtain an accurate measurement, and the overall time will be divided by the number of repeats. The time for the generalised pingpoing is the time to send p(p-1) messages of length n and can be analysed in the same way as COMMS1 and COMMS2 into values of  $(r_{\infty}, n_{\frac{1}{2}})$ . The value obtained for  $r_{\infty}$  is the required total saturation bandwidth, and we are interested in how this scales up as the number of processors p increases and with it the number of available links in the system.

COMMS3 is a new benchmark written specifically for PARKBENCH.

#### 3.3.3 Communication Bottleneck: POLY3

POLY3 assesses the severity of the communication bottleneck. It is the same as the POLY1 benchmark except that the data for the polynomial evaluation is stored on a neighbouring processor. The value of  $f_{\frac{1}{2}}$  obtained therefore measures the ratio of arithmetic to communication performance. Equation (3.3) shows that the computational intensity of the calculation must be significantly greater than  $f_{ij}$  (say 4 times greater) if communication is not to be a bottleneck. In this case the computational intensity is the ratio of arithmetic performed on a processor to words transferred to/from it over communication links. In the common case that the amount of arithmetic is proportional to the volume of a region, and the data communicated is proportional to the surface of the region, the computational intensity is increased as the size of the region (or granularity of

Table 3.1: Current Low-Level benchmarks and the Parameters they measure. Note we abbreviate performance (perf.), arithmetic (arith.), communication (comms.), operations (ops.).

| Benchmark        | Measures                 | Parameters                            |  |  |  |  |

|------------------|--------------------------|---------------------------------------|--|--|--|--|

| SINGLE-PROCESSOR |                          |                                       |  |  |  |  |

| TICK1            | Timer resolution         | tick interval                         |  |  |  |  |

| TICK2            | Timer value              | wall-clock check                      |  |  |  |  |

| RINF1            | Basic Arith. ops.        | $(r_{\infty}, n_{\frac{1}{2}})$       |  |  |  |  |

| POLY1            | Cache-bottleneck         | $(\hat{r}_{\infty}, f_{\frac{1}{2}})$ |  |  |  |  |

| POLY2            | Memory-bottleneck        | $(\hat{r}_{\infty}, f_{\frac{1}{2}})$ |  |  |  |  |

| MULTI-PROCESSOR  | {                        |                                       |  |  |  |  |

| COMMS1           | Basic Message perf.      | $(r_{\infty}, n_{\frac{1}{2}})$       |  |  |  |  |

| COMMS2           | Message exch. perf.      | $(r_{\infty}, n_{\dagger})$           |  |  |  |  |

| COMMS3           | Saturation Bandwidth     | $(r_{\infty}, n_{\frac{1}{2}})$       |  |  |  |  |

| POLY3            | Comms. Bottleneck        | $(\hat{r}_{\infty}, f_{\frac{1}{2}})$ |  |  |  |  |

| SYNCH1           | H1 Barrier time and rate |                                       |  |  |  |  |

the decomposition) is increased. Then the  $f_i$  obtained from this benchmark is directly related to the granularity that is required to make communication time unimportant.

POLY3 is a new benchmark written specifically for PARKBENCH.

# 3.3.4 Synchronisation Benchmarks: SYNCH1

SYNCH1 measures the time to execute a barrier synchronisation statement as a function of the number of processors taking part in the barrier. The practicability of massively parallel computa-

tion with thousands or tens of thousands of processors depends on this barrier time not increasing too fast with the number of processors. The results are quoted both as a barrier time, and as the number of barrier statements executed per second (barr/s).

The SYNCH1 benchmark exists as part of Genesis v2.1.1 [20].

### 3.4 Summary of Benchmarks

Table 3.1 summarises the current low-level benchmarks, and the architectural properties and parameters that they measure.

## Chapter 4

# Kernel Benchmarks\*

#### 4.1 Introduction and Rationale

The low-level benchmark codes are designed to measure the basic architectural features of parallel machines. Full application codes obviously measure the performance of a parallel system on the full problem and this is ultimately what the user wants. However, in many instances, the full application codes are complex, contain many 100s of thousands of lines of Fortran, and are not available in a suitable parallel version. In order to obtain a guide to the performance of any given parallel system on a particular application something less complex than the full application is useful. A profile of the sequential version of the application enables the compute intensive portions of the program to be identified. It is these computeintensive sections of an application that we wish to model with the introduction of parallel kernel benchmarks.

The popular kernel benchmarks that have been used for traditional vector supercomputers, such as the Livermore Loops [9], the LINPACK benchmark [12] and the original NAS kernels [31], are clearly inappropriate for the performance evaluation of parallel machines. The tuning restrictions of these benchmarks rule out many widely used parallel extensions. More importantly. the computation and memory requirements of these programs do not do justice to the vastly increased capabilities of the new parallel machines. particularly those that will be available by the mid 1990's. For these reasons we believe that a new. widely accepted set of kernel benchmarks is desirable as a step on the way to more sensible and scientific performance reporting of parallel systems.

The kernel codes are typically up to a few thousand lines of Fortran and are sufficiently simple that the performance of a given parallel machine