## Hybrid statistical and recurrent neural network architecture implementation in FPGA device used for severe acute respiratory syndrome coronavirus detector

V.M. Senthilkumar<sup>a,\*</sup>, S. Thenmozhi<sup>b</sup>, M.V. Kumudavalli<sup>c</sup> and U. Yedukondalu<sup>d</sup>

<sup>a</sup>Department of ECE, Vivekanandha College of Engineering for Women (Autonomous), Namakkal, Tamilnadu, India

<sup>b</sup>Department of ECE, Dayananda Sagar College of Engineering, Bangalore, Karnataka, India

<sup>c</sup>Department of Computer Applications, Dayananda Sagar College of Arts Science and Commerce, Bangalore, Karnataka, India

<sup>d</sup>Department of ECE, MVR College of Engineering & Technology (Autonomous) Paritala, Andhra Pradesh, India

**Abstract**. The Severe Acute Respiratory Syndrome (SARS) are caused by the strain of the corona virus causes cold and influenza. In recent years, the covid pandemic spread throughout the world killing millions of people. The fatality rate has increased and it also leads to pneumonia for breathing problems. Several methods like wavelet filter banks, time series methods, Neural networks was developed for the diagnosis of severe acute respiratory syndrome coronavirus, still the accuracy can be improved. Less works is carried out for hardware implementation for syndrome detectors. This proposed work represents the FPGA (Field Programmable Gate Array) implementation of the hybrid method using Convolutional Recurrent neural network and Independent Components Analysis (ICA). The architecture extracts the complex features from ECG (Electrocardiogram) samples. The hybrid Statistical and Recurrent Neural Network (RNN) Architecture implemented in MATLAB, Embedded and DSP (Digital Signal Processor). But, the FPGAs consume less power computationally efficient. Since, ICA is an efficient method due to its blind source separation property accumulate the extraction of features accurate described. The mathematical model for the analysis of ECG signal using RNN is analyzed and based on that the proposed model is selected. On investigation the hybrid method using the statistical and neural network model is efficient in the analysis of biomedical signal especially ECG. The proposed ICA based RNN model is mathematically evaluated and tested with real time data. For implementation, Quartus software is used for effectiveness of the proposed model.

Keywords: Field programmable gate array, recurrent neural network, independent component analysis, electrocardiogram, severe acute respiratory syndrome

\*Corresponding author. V.M. Senthilkumar, Department of ECE, Vivekanandha College of Engineering for Women (Autonomous), Namakkal, Tamilnadu, India. E-mail: vmssenthilece@gmail.com.

#### 1. Introduction

The Severe acute respiratory syndrome (SARS) outbreak in china has created panic among people once the disease is identified to be deadly. Caused by the strain of the corona virus causing common cold.

ISSN 1064-1246 © 2023 – The authors. Published by IOS Press. This is an Open Access article distributed under the terms of the Creative Commons Attribution-NonCommercial License (CC BY-NC 4.0).

The viral respiratory disease is dangerous if identified. Most of the countries are suffered due to the spread of the SARS-associated coronavirus. Since February 2003 the spread was higher still today due to its variants. This airborne virus causes cold and influenza. In recent years, the covid pandemic even after restriction of international air travel have slowly spread through the world killing millions of people. Children under 15 years are also affected and the fatality among persons with illness is higher. The symptoms are fever of 100.5° F, dry cough, shortness of breath. Since, the symptoms may be SARS leads to a breathing problems. The wearing of mask and gloves may prevent the spread but, once infected it should be treated properly. Wavelet filter banks, RNN and ICA was developed for the diagnosis of severe acute respiratory syndrome coronavirus. The complex features were extracted from ECG samples. The extracted features were planned to feed the features to the RNN classifier to differentiate between severe acute respiratory syndrome coronavirus, pneumonia, and normal cases.

Severe acute respiratory syndrome coronavirus dataset is utilized for the experiments for training and testing. Due to the uncorrelated and inconsistency of dataset, severe acute respiratory syndrome coronavirus images were difficult to classify. The data insufficiency may lead to over or under-classification. The main contribution of the work is designing a Hybrid Statistical and Recurrent Neural Network Architecture and its implementation in a real time hardware. The hardware not only detects the Severe Acute Respiratory Syndrome Coronavirus Detector but can be used for other application with certain modification. The proposed method can be implemented in MATLAB, Embedded and DSP processor. But, the FPGAs consume less power and computationally efficient. Since ICA is an efficient method due to its blind source separation property, the extraction of features is accurate. The algorithm separates the image sources which are statistically independent, which is the important advantage of the method. The algorithm is computationally efficient. The proposed method or network for severe acute respiratory syndrome coronavirus classification contains the following steps.

**Step 1:** Initialize the CNN model parameters; **Step 2**: Framing the feature map as input; **Step 3**: multi-layered network input assignment; **Step 4**: Classification of data. The data used are free from environmental noise signals. Accordingly, the separate filtering is not required for preprocessing. The early stopping and low noise images were used to avoid overfitting.

#### 2. Literature survey

In literature, several systems are designed for Recurrent Neural Network (Walid Zgallai et al, 2012). Acquisition unit designed for electrocardiogram (ECG) on system-on-a-chip (SoC) architecture with IEEE 802.15.4 ZigBee system are efficient but, the data rates are very poor. In ECG system, which is CMOS based high speed device working at 2.4-GHz designed using TSMC 0.18-µm [1]. In other work, to detect QRS complex in electrocardiogram (ECG) delta modulator was designed. The ECG analysis using maximum and minimum point methods were made, and Xilinx Spartan-6 FPGA is used based on CMOS technology design for wearable ECG recording devices [2]. Sensor ICs were designed by Jiang et al, 2016 [3], which is designed using CMOS processing and control approach. The ultrathin sensing array has 256 elements in the unit and the power consumptions are managed by proper driving circuits [7].

Designing algorithms for IC implementation is a challenging task for proposed model. Wavelet transform based methods occupy lesser memory but, efficient in working for all control analyzing process for detecting corona virus. Complex features diagnosis can be extracted using wavelet transform described and established in [4, 17]. The wavelet transform is efficient for other biomedical application like pressure detection and body infection estimated in [5]. Nowadays, the ECG multiple features analysis for biological recognition system are commonly presented. The feature extraction methods using the linear discriminant analysis (LDA) provides higher recognition rates but, the hardware utilization should be optimized and simulated [6]. Amplifiers are required to increase the strength of biomedical signal, which is designed by op-amps recommended by FPGA kit [18, 19].

CMOS are used for both low power and high power sensor applications to detect the optical and spectrum sensing signals [8]. To detect other life-threatening disease like ST elevation myocardial convolutional neural network were proposed. The device acquires ECG from 12-lead electrode setup verified. The preprocessing data was performed by using a band pass filter with power line removal notch filter. The Receiver Operating Characteristic (ROC) was varied according to the preprocessing level. QRS processor designs are used in this literature for portable mobile device. In this design was done by 180 nm CMOS technology [9]. In recent years, Field programmable gate array were widely used for artificial neural network implementation for biomedical applications. Arrhythmia are detected using this device described by Zairi et al., 2020 [13].

Since, the deep learning methods were effectively implemented in many software's [11]. The contribution of this paper is hardware implementation, which is less performance in Adaptive hardware communication, modulation signal, and image processing signal applications. Genetic algorithm based hardware were utilized in classification process. Even though, it is found effective in the accuracy. When there is more noise signal received and proposed (Zhu et al, 2019) [10]. The artifacts can be removed to improve the accuracy evaluated [14]. Custom DSP hardware's for Hamilton-Tompkins (HT) algorithm in ECG signal analysis the data compression was presented. For compression of ECG data, biorthogonal wavelet transform was used. Certain methods are implemented in Walsh function based CNN for heart beat classification. There is also fast computing but, the area occupied will be more presented [16, 20, 21].

To remove the EOG (Electro-Oculogram) noise from the EEG signal (Electroencephalography) was developed a method based on singular spectrum analysis (SSA) and adaptive noise canceler (ANC). The reference signal for the adaptive filter was obtained by grouping techniques. Tsoutsouras, V, Koliogeorgi, K., Xydis, S et al., 2017, presented [15] a novel method for extract the focal and non-focal element groups of the EEG signal. The fractal behavior during morphological changes in focal and non-focal EEG signals were utilized for presurgical intervention by using inspection virus scan analysis. The proposed FPGA used SARSCD (Serve Acute Respiratory Syndrome Coronavirus Detector) is implemented in hybrid methods. Which is find out very short term using real-time virus database [8, 25].

#### 3. Background methodology

In the above literature, there are several work investigations on hardware architecture for removal of noise, feature extraction and classification for other biomedical signals. The prototype model used to time, frequency and scaling transform identifications. As the proposed work focuses on hybrid statistical

and machine learning approach. Adaptive filters were good in noise removal and it is easily implemented in hardware but, which is achieved proper convergence and higher noise rejection optimal in order to chosen properly. The complex task without hybrid system using real-time database is implement and developed in [12]. The existing methods were simulated using MATLAB code composer studio and python programming language. The performance of singular value decomposition, wavelet transform, and other methods were effectively described. When the software concerns to control and implement in easy way for identify the virus detection [22]. The fetal monitoring system were reported, which is effective using statistical methods. But, the device area will increase due to the higher computation blocks. The extraction process was accurate compared to other methods. In this extractions method can be implemented using summer, subtractors, registers, and accumulator processing.

In any diagnosis process includes preprocessing, feature detection, and classification approach. Before, the process begins noise is removed and feature extraction using to various stage method for diagnosis the virus. Normalization of data is carried out in few cases. The features under investigation and extraction are the shape, edge, gray texture, frequency-based texture, second order statistical features, and local training models. In this other, the point of interest is covariant region sum identifying data to extract the proposed system. In Computed Tomography (CT) dilated segmental, sub-segmental vessels, and the bilateral areas of ground-glass opacities are analyzed using feature extraction. The Region of Interest (ROI) is extracted to machine learning and artificial intelligence methods are effective in the process. The methods need large data set for training and testing. A Long short-term memory (LSTM) uses to class labels for classifications methods. The network structure retains the past values and events the time-series prediction. The past or historical data are retained through the LSTM network. The major blocks in the structure are input gate, forget gate, output gate, and cell unit were updated. The updating of information is done regularly in this scheme.

## 3.1. GPU hybrid acceleration platform for recurrent neural networks

The computation throughput in batch deep neural network can be improved by using the GPUaccelerated platform. For small batch RNN, there is degradation in the performance. For irregular input sequences the large batch size is not appropriate. The performance is poor for partial retraining and low latency. The challenges increase, when RNN designed for mobile devices due to low utilization especially for small-batch sizes. FPGA device can be optimized for to suitable with GPU accelerated RNN method. The other challenges are occupying computational overhead for nonlinear data. But, the medical application in the input data is predictable and linear at most cases there is less complexity in the design.

## 3.2. Recurrent neural network structure for VLSI implementation

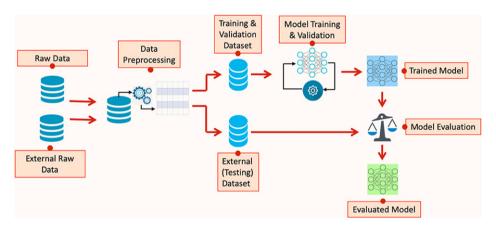

Recurrent neural network can handle complex and nonlinear data. Which can be sequential due to the presence of more feedback loops. The long-term time dependency on the data sequence can be handled well by RNN. That's the reason it is used in biomedical data analysis where the data are longer sequences and time based. For any network, the input can be (x1,...,xt), fed to network on a fixed sized vector and output would be (y1,...,yt) which is obtained using the softmax mapping function. The input and output sequence structure on the Recurrent neural network structure is presented below in Fig. 2.

Conventional methods for implementing the existing RNN suffers from learning problems in training. If the sequence is longer and there is deviation exponentially related on the gradient vector. Need of memory to store states is the main challenges. The gates on input for forget the outputs are same at each time. To avoid this problem on longer sequence and the time based dependency Long Short-Term Memory (LSTM) can be used. So, the longer sequences of the biomedical system can be stored in a separate memory cell. Apart from that the gates namely input values or outputs gate needs the memory cell and hidden state. The data sequence and proposed states are stored in the memory for retrieval, analysis, and other functions described.

# 4. Proposed method development of hybrid statistical and recurrent neural network architecture implementation

Transfer Learning is adopted due to the lag on data to train the parameters. To enhance this, the proposed architecture has fully-connected layers and convolutional filter presented. The statistical ICA unit and Max-pooling VLSI architecture is designed. Architectures in FPGA are difficult to implement for Dense Convolutional Network (DenseNet) due to complex form of hidden layers. Even though InceptionV3 has network depth to handle resources, and the building block requirement is additionally in FPGA kit. Designing proper hardware to max-pooling unit improves the dimensionality reduction. Deep learning Methods like Inception-ResNetV2 with higher deep layers were designed using the residual connections of inception structures. The convolution filters were designed to handle image dataset.

#### 4.1. Development of ICA-RNN hybrid network

A hybrid network based on statistical ICA and RNN is proposed in this work for the diagnosis of Severe Acute Respiratory Syndrome Coronavirus. The method was developed for FPGA. The hybrid network is comparable with existing DeneNet121, VGG19, Inception-ResNetV3 and InceptionV3. The network is designed so to classify between SARS Coronavirus, pneumonia, and normal cases. The linear mixture of sources which are statistically independent is separated using the Independent component analysis (ICA) method. The diagnosis process includes the separation of physiological signal from various sources to be statistically independent and form a linear mixture. In blind source separation method, the physiological data are separated based on the source signals. The assumptions are that the medical sources are independent so as to apply the ICA method.

Mixing matrix is given by,

$$(A) = \begin{pmatrix} a1, 1 \ a1, 2 \dots a1, n \\ a2, 1 \ a2, 2 \dots a2, n \\ \vdots \\ an, 1 \ an, 2 \dots an, n \end{pmatrix}$$

The physiological data  $x_i(t)$  is given by,

$$x_{i}(t) = \sum_{j=1}^{m} a_{ij}(t) s_{j}(t), \qquad i = 1, 2, 3 \dots n$$

(1)

or as a matrix decomposition,

$$X = AS \tag{2}$$

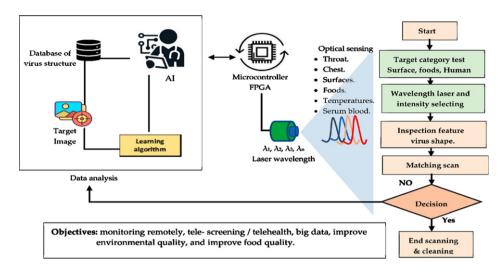

Fig. 1. (a). Proposed FPGA Device Used Acute Respiratory Syndrome Coronavirus Detector.

Fig. 1. (b). Block diagram of the various stages of deep learning diagnosis method.

The various parameters like separation matrix W, A (i.e. W = A-1), matrix S independent are computed.

$$S = WX \tag{3}$$

The independence nature of physiological signal is found using the entropy using the INFOMAX algorithm. ICA algorithm find the physiological sources S based on the maximum entropy observed. The independent physiological sources are identified one by one using the BSS method.

From the INFOMAX algorithm the change on W, is given by

$$W = \Delta w \alpha [I - \varphi(u)uT] \tag{4}$$

Where,  $\varphi(.)$  is the nonlinear transfer function given by Equation (5). 'U' is the output vector of the neural network.

$$\varphi(ui) = \frac{e^{u_i} - e^{-u_i}}{e^{u_i} + e^{-u_i}}$$

(5)

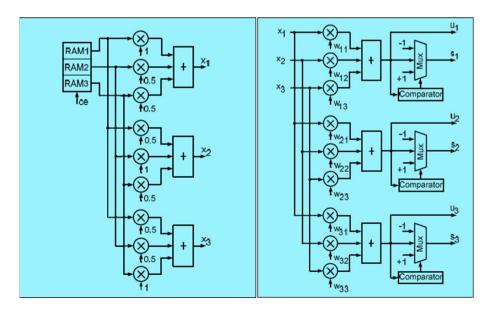

#### 4.2. FPGA implementation of ICA algorithm

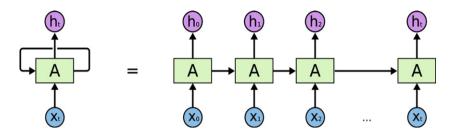

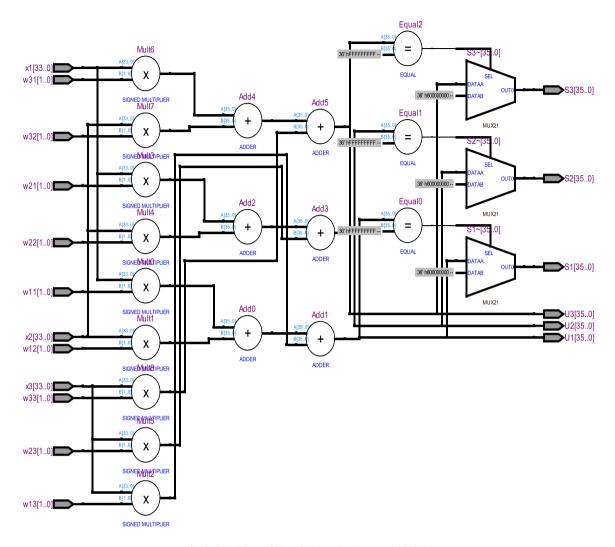

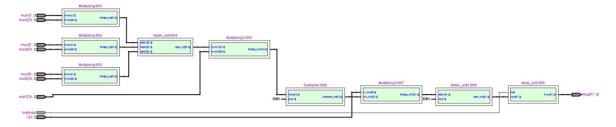

The various blocks of the ICA method for three inputs are shown in Fig. 1; The multiplexer is designed for the learning block,

#### 4.3. Mixer subsystem

The independent signals S are input stored in memory. The subsystem handles the mixing matrix A

Fig. 2. RNN structure.

Fig. 3. ICA digital system.

and X. shown,

$$\begin{bmatrix} x_1 \\ x_2 \\ x_3 \end{bmatrix} = \begin{bmatrix} 1 & 0.5 & 0.5 \\ 0.5 & 1 & 0.5 \\ 0.5 & 0.5 & 1 \end{bmatrix} * \begin{bmatrix} S_1 \\ S_2 \\ S_3 \end{bmatrix}$$

(6)

The mixer unit performs the process according to Equation (6). The gate level logic of the mixing pro-

cess is shown in Fig. 2. In that subsystem, the input signals are stored in the RAM unit. The input signals are multiplied by matrix elements and produces the observing matrix 'X'.

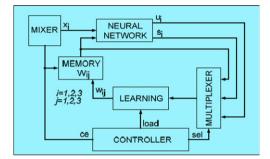

#### 4.4. Neural network

The implementation is done for linear function due to the complexity in hyperbolic tangent.

$$s = \begin{cases} -1 & u \le -1 \\ u & -1 < u < +1 \\ +1 & u \ge +1 \end{cases}$$

The circuit diagram of the neural network is shown in diagram in Fig. 4(b). The convolution layers and pooling layers are implemented using this block (Fig. 4). The feature maps are multiplexed. The original kernel weights are also selected and summed as shown. The architecture in the pooling layer is optimized by eliminating redundancy so the CNN control

Fig. 4. Blocks of proposed method (a) Mixing of Matrix in ICA algorithm (b) Processing element Neural Network.

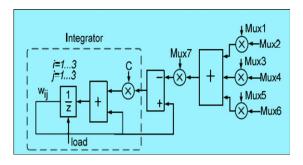

Fig. 5. Learning subsystem.

block reduces in area. The non-friendly floating-point values are converted to normalized values through quantization and fusion before applying the CNN process. Accordingly, the hardware follows a symmetric quantization to do it on weights and feature maps. The CNN control block with the quantization unit performs the major functions using the processing element of neural network. The CNN control block is optimized by converting all layers into a standard convolution layers, which contains the original loop computation. By this process only one standard PE(Processing Element) is enough to perform all convolution layer computations.

#### 4.5. Learning subsystem

Figure 5 shows the circuit diagram of the learning subsystem for FPGA. The number of DSP units required to implement in FPGA are 58. But the count can be reduced using multiplexing. Table 1 shows the selection lines with the parameters selected.

#### 4.6. Controller

This sub block generates the sel, load, and ce lines for the simulation circuit. Controller block manages the flow of data between the blocks of the neural network, mixer and other units. Even though the sampling frequency of the biomedical signal is less, proper synchronization is required. The control involves multiplexing the inputs, reading data from memory and sending data to output.

#### 5. Results and discussion

The implementation of a hybrid architecture for SARS diagnosis using ICA was optimized using the RNN data analysis is done in FPGA. There were several issues in the design of diagnosis device for SARS using Very Large Scale Integration. Errors will create large problems in therapy and is avoided in clinically diagnostic environment. For the implementation adders, multipliers, delay elements, and multiplexer were used. This optimized designs for the is less area and low power consumption since implemented using various FPGA kits. The implementation of the biomedical processing algorithm in Field Programmable Gate Array (FPGA) involves large number of Look Up Tables (LUTs). From the Tables 1-4 it can be observed that the number of LUTs, power dissipation and delay vary for various devices. The development and validation of programming lines were done using workbenches so that the blocks can be implemented in SOC through library functions in future. The SARS algorithms were not implemented in literature and the existing DSP algorithms of ICA and NN were slower and consumes more power.

The Tables show the advantages of the proposed system with low power and optimized performance on delay and LUT. The proposed RNN -ICA the convergence behavior of the architectures. The proposed method reduces the area and power consumption. The main contribution towards a design of compact, battery operated, low power device is made through Very Large Scale Technology. If implemented System On Chip Architecture (SoC) design, the power

| Table 1                       |

|-------------------------------|

| Multiplexers and their inputs |

| Sel (3:0) | Mux1 | Mux2 | Mux3 | Mux4 | Mux5 | Mux6 | Mux7 |

|-----------|------|------|------|------|------|------|------|

| 0000      | w11  | u1   | w12  | u2   | w13  | u3   | s1   |

| 0001      | w12  | u2   | w11  | u1   | w13  | u3   | s2   |

| 0010      | w13  | u3   | w11  | u1   | w12  | u2   | s3   |

| 0011      | w21  | u1   | w22  | u2   | w23  | u3   | s1   |

| 0100      | w22  | u2   | w21  | u1   | w23  | u3   | s2   |

| 0101      | w23  | u3   | w21  | u1   | w22  | u2   | s3   |

| 0110      | w31  | u1   | w32  | u2   | w33  | u3   | s1   |

| 0111      | w32  | u2   | w31  | u1   | w33  | u3   | s2   |

| 1000      | w33  | u3   | w31  | u1   | w32  | u2   | s3   |

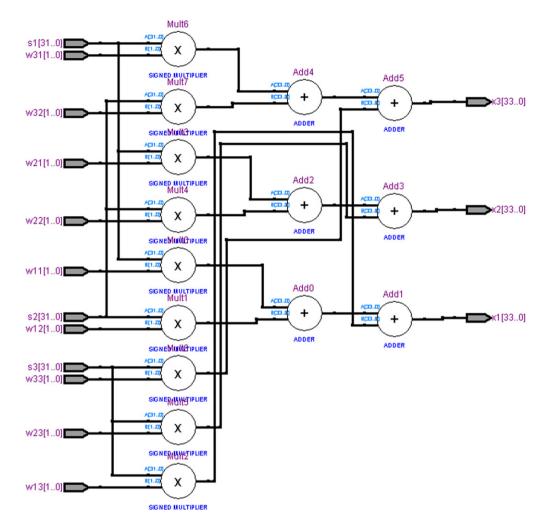

Fig. 6. RTL View of Mixer Subsystem [23, 24].

consumption can be further reduced. In addition, the FPGA-based prototyping can be converted to library for future uses. The existing and proposed algorithms presented in this work are implemented using the Quartus Software in FPGA based on 65 nm and 90 nm CMOS process. The methods are compared for power, delay and LUT. The implementation was done using Cyclone and Stratix kit. The RTL view of the different blocks are shown from Fig. 6 to and Fig. 14. The FPGA implementation was done with altera's cyclone II 90 nm and Cyclone III 65 nm device. The industrial grade cyclone II 90 nm and Cyclone III 65 nm FPGA works on 1.2 and 0.9 V respectively. These low power devices provide even 200,000 logic elements (LE's). The static power is about 1/4 watt of static power consumption. The FPGA implementation was carried out with of 180,000 logic elements in Stratix III 65-nm CMOS process. The parameters

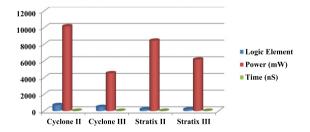

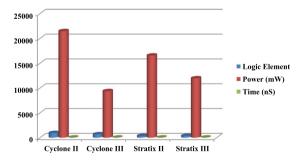

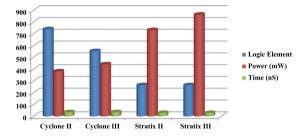

Fig. 7. Parameter analysis of Mixer Subsystem in different nm technologies.

like power, delay and LUT are compared for different blocks of the existing and proposed method. From the results in VLSI, the robustness is checked with respect to power consumption and area which is the number of logic elements.

| technologies |               |            |           |  |

|--------------|---------------|------------|-----------|--|

| FPGA Family  | Logic Element | Power (mW) | Time (nS) |  |

| Cyclone II   | 704           | 10168.77   | 22.512    |  |

| Cyclone III  | 483           | 4530.44    | 20.174    |  |

| Stratix II   | 204           | 8443.38    | 19.993    |  |

| Stratix III  | 204           | 6180.61    | 20.587    |  |

Table 2 Parameter analysis of Mixer Subsystem in different nm technologies

#### 5.1. Mixer subsystem

The implementation of the mixer subsystem was done using Cyclone and Stratix kit. The RTL view showing the internal blocks of mixer system is presented in Fig. 6. There are 9 multipliers and 4 adders designed and used in this unit. The performance of the mixer subsystem block is shown in Table 2. The coefficient and inputs namely the 's' and w' respectively are mixed for the ICA operation and finally the components are obtained as shown in Fig. 6. From Table 2 it can be observed that the number of logic elements, power and delay are more in the 90 nm CMOS based Cyclone II kit. While the 65 nm CMOS kits in both Cyclone III and Stratix III shows low power and a smaller number of logic elements. The robustness is measured with the number of the logic elements and power is very less. Hence, the real-time data base virus detection is very simple in this proposed work.

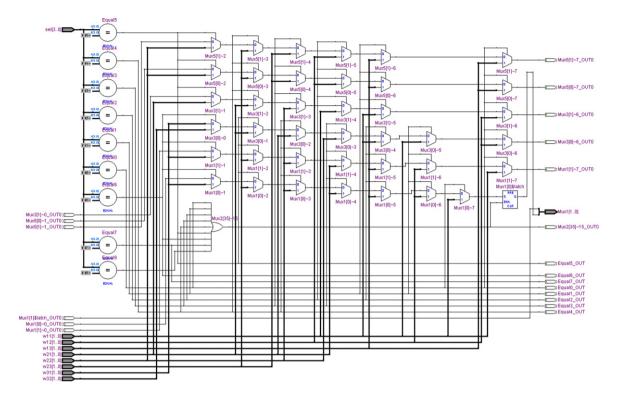

#### 5.2. Neural network subsystem

Similarly, the implementation of the Neural Network subsystem using the processing elements like adders, multipliers was done by using Cyclone and Stratix kit. The RTL view showing the internal blocks of mixer system is presented in Fig. 8. The block consists of comparators, adders, multipliers and multiplexers. Figure 9 shows the parameter comparison which represents the robustness of the devices in various technologies for power, delay and area. The performance of the neural network subsystem block is shown in Table 3. The inputs namely the 'x' and w' are processed for neural network training. From Table 2 it can be observed that the number of logic elements, power and delay are more in the 90 nm CMOS based Cyclone II kit. While the 65 nm CMOS kits in both Cyclone III and Stratix III shows low power and less number of logic elements. The robustness is measured with the number of the logic elements, delay and power.

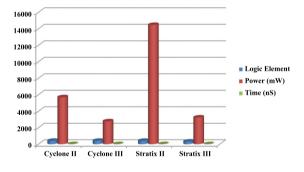

#### 5.3. Multiplexer subsystem

The multiplier subsystem which occupies the maximum area is shown in Fig. 10. The unit is designed using the D flip-flop, Multiplexers. The block consists of comparators at the input side, and multiplexers. The data passing through the unit is data driven using clock units. Figure 11 shows the parameter comparison, which represents the robustness of the devices in various technologies for power, delay and area. The performance of the neural network subsystem block is shown in Table 4. From Table 4 it observed that the number of logic elements, power, and delay are extra in the 90 nm CMOS based Cyclone II kit. While the 65 nm CMOS kits in both Cyclone III and Stratix III shows low power and a smaller number of logic elements. The Stratix device shows better delay. The robustness is measured with the number of the logic elements, delay, and power. Therefore, the virus detection is very simple in this proposed work.

#### 5.4. Learning subsystem

The implementation of the learning subsystem using the processing elements like adders and multipliers was done using Cyclone and Stratix kit. The RTL view showing the internal blocks of learning system is presented in Fig. 12. The block consists of comparators, adders, multipliers and multiplexers. Figure 13 shows the parameter comparison, which represents the robustness of the devices in various technologies for power, delay and area. The performance of the block is shown in Table 5. The inputs taken from previous blocks are processed for learning and training. From Table 5 it can be observed that the number of logic elements, and delay are more in the Cyclone kits than Stratix. While the power in cyclone kit for this block is less. The robustness is measured with the number of the logic elements, delay, and power.

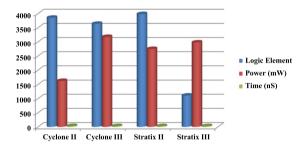

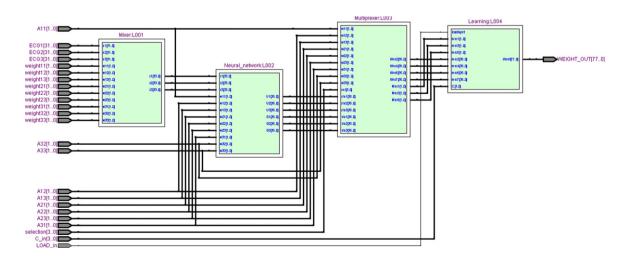

#### 5.5. Implementation of proposed algorithm

The proposed hybrid network is implemented by the various processing units of ICA and RNN in FPGA. The architecture consists of blocks like mixing unit, multiplexer, learning units which will separate the sources which are statistically independent. The inputs are acquired and converted to digital form. The input bit streams are given to the circuit. The diagnosis process based on separation of physiological signal from various sources to be sta-

Fig. 8. RTL View of Neural Network subsystem [23, 24].

Fig. 9. Parameter analysis of Neural Network in different nm technologies.

tistically independent and form a linear mixture are done in digital circuit. The implementation of the proposed algorithm is done by combining various blocks, which are implemented and tested separately. The

Table 3

Parameter analysis of Neural Network in different nm technologies

| e           |               |            |           |  |  |

|-------------|---------------|------------|-----------|--|--|

| FPGA Family | Logic Element | Power (mW) | Time (nS) |  |  |

| Cyclone II  | 934           | 21459.25   | 27.844    |  |  |

| Cyclone III | 675           | 9367.53    | 24.338    |  |  |

| Stratix II  | 351           | 16546.66   | 29.754    |  |  |

| Stratix III | 360           | 11953.64   | 23.935    |  |  |

RTL view showing the internal blocks of learning system is presented in Fig. 14. The block consists of comparators, adders, multipliers and multiplexers. Figure 15 shows the parameter comparison which represents the robustness of the devices in various technologies for power, delay, and area.

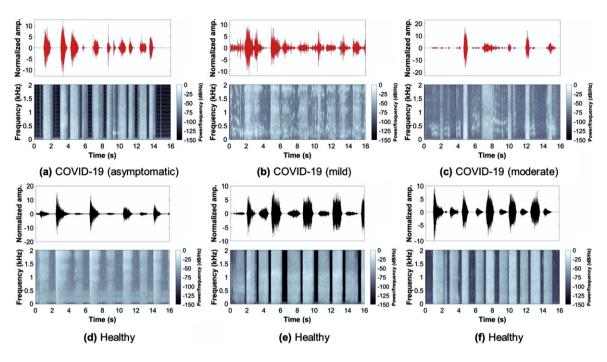

Figure 16 is shows that proposed model spectrograms detect breathing sounds form the real-time

Fig. 10. RTL view of multiplexer subsystem.

Fig. 11. Parameter analysis of Multiplexer Subsystem in different nm technologies.

Table 4 Parameter analysis of Multiplexer Subsystem in different nm technologies

| e           |               |            |           |  |

|-------------|---------------|------------|-----------|--|

| FPGA Family | Logic Element | Power (mW) | Time (nS) |  |

| Cyclone II  | 412           | 5692.12    | 11.133    |  |

| Cyclone III | 412           | 2770.56    | 10.472    |  |

| Stratix II  | 406           | 14462.98   | 10.517    |  |

| Stratix III | 321           | 3237.24    | 5.765     |  |

|             | 521           | 5257.21    | 5.70      |  |

database. The performance of the block is shown in Table 6. From Table 6 it shows that the number of logic elements utilized for the proposed method implementation in Stratix III is very less. The delay is almost same in all devices. The power has drastic variations in all four devices. The robustness is measured with the number of the delay, logic elements and power. The disadvantage of the method is that the method is to be optimized if implemented in ASICs (Application specific integrated circuit). Since, the ASICs the chip area is to be minimum, implementing ICA method will consume more area. But, the architectures for the proposed method will reduce the area compared to the conventional methods.

#### 6. Conclusion

In this paper, a hybrid statistical and recurrent neural network architecture implementation in FPGA device used for severe acute respiratory syndrome coronavirus detector is presented. SARS available is identified by extracting the complex features from ECG samples. The extracted features are analyzed. Implementation of the method and testing with real time data is made. The proposed method uses the advantages of ICA and RNN. On investigation the hybrid method using the statistical and neural network ICA based RNN method model is efficient in the analysis of biomedical signal. For implementation,

Fig. 12. RTL View of Learning Subsystem [23, 24].

Fig. 13. Parameter analysis of Learning Subsystem different nm technologies.

Table 5 Parameter analysis of Learning Subsystem different nm technologies

| 6           |               |            |           |  |

|-------------|---------------|------------|-----------|--|

| FPGA Family | Logic Element | Power (mW) | Time (nS) |  |

| Cyclone II  | 739           | 381.28     | 35.483    |  |

| Cyclone III | 553           | 440.67     | 35.197    |  |

| Stratix II  | 264           | 731.31     | 28.507    |  |

| Stratix III | 264           | 862.48     | 28.685    |  |

Fig. 15. Parameter analysis of proposed algorithm in different nm technologies.

Quartus software is used. The architecture proposed for SARS analysis can be implemented for SOC with electrode selection unit, analog to digital converter, processing units and digital to analog converter. In future, many application specific integrated circuits for the proposed design will be modified and developed. This will reduce the cost, if mass production is made by detection of virus that is available in the realtime virus database. A new device like FinFET will

Fig. 14. RTL View of proposed algorithm.

Fig. 16. Corresponding spectrograms detect breathing sounds form the real-time virus database.

Table 6 Parameter analysis of proposed algorithm in different nm technologies

| FPGA Family | Logic Element | Power (mW) | Time (nS) |

|-------------|---------------|------------|-----------|

| Cyclone II  | 3856          | 1628.24    | 33.878    |

| Cyclone III | 3641          | 3176.98    | 30.149    |

| Stratix II  | 3986          | 2750.54    | 29.930    |

| Stratix III | 1110          | 2981.11    | 28.517    |

be incorporated for the design. The proposed design of advance memory elements is to be intended for storing of processing data.

#### References

- L. Wang, T. Chen, K. Lin, Q. Fang and S. Lee, For IEEE 802.15.4 Implementation of a Wireless ECG Acquisition SoC (ZigBee) Applications, in *IEEE Journal of Biomedical and Health Informatics* 19(1) (2015), 247–255, Doi: 10.1109/JBHI.2014.2311232.

- [2] X. Tang, Q. Hu and W. Tang, A Real-Time QRS Detection System with PR/RT Interval and ST Segment Measurements for Wearable ECG Sensors Using Parallel Delta Modulators, in *IEEE Transactions on Biomedical Circuits and Systems* **12**(4) (2018), 751–761, Doi: 10.1109/TBCAS.2018.2823275.

- [3] H. Jiang, Z. Wang, S. Yang, H. Liu and Z. Wang, CMOS wireless stress sensor IC with 256-cell sensing array for ultra-thin applications, *Electron. Lett.* 52(20) (2016), 1660– 1661.

- [4] P. Li et al., A low-complexity ECG processing algorithm based on the Haar wavelet transform for portable health-care devices, *Sci. China Inf. Sci.* 57(14) (2014).

- [5] P. Li, M. Liu and X. Zhang, Novel wavelet neural network algorithm for continuous and noninvasive dynamic estimation of blood pressure from photo-plethysmography, *Sci. China Inf. Sci.* 59(4) (2016).

- [6] Y. Miao, Y. Tian, L. Peng, M.S. Hossain and G. Muhammad, Research and Implementation of ECG-Based Biological Recognition Parallelization, in *IEEE Access* 6 (2018), 4759– 4766, Doi: 10.1109/ACCESS.2017.2771220.

- [7] Murugesan, Malathi, Kaliannan, Kalaiselvi, Balraj, Shankarlal, Singaram, Kokila, Kaliannan, Thenmalar and Albert, Johny Renoald, A Hybrid Deep Learning Model for Effective Segmentation and Classification of Lung Nodules from CT Images, *Journal of intelligent and fuzzy system* 42(3) (2021), 2667–26791. DOI: 10.3233/JIFS-212189.

- [8] S. Yaman, B. Karakaya and Y. Erol, A novel normalization algorithm to facilitate pre-assessment of Covid-19 disease by improving accuracy of CNN and its FPGA implementation. *Evolving Systems* (2022). https://doi.org/10.1007/s12530-022-09419-3

- [9] P. Li et al., A 410-nW Efficient QRS Processor for Mobile ECG Monitoring in 0.18-µm CMOS, in *IEEE Transactions* on Biomedical Circuits and Systems **11**(6) (2017), 1356– 1365, Doi: 10.1109/TBCAS.2017.2731797.

- [10] W. Zhu, X. Chen, Y. Wang and L. Wang, Arrhythmia Recognition and Classification Using ECG Morphology and Segment Feature Analysis, in *IEEE/ACM Transactions on Computational Biology and Bioinformatics* 16(1) (2019), 131–138, Doi: 10.1109/TCBB.2018.2846611.

- [11] K. Hanbay, Deep neural network based approach for ECG classification using hybrid differential features and active learning, in *IET Signal Processing* 13(2) (2019), 165–175, Doi: 10.1049/iet-spr.2018.5103.

- [12] S. Ravindrakumar and K. Bommannaraja, Certain investigation on De-noising the multichannel abdominal ECG signal using various adaptive noise suppression techniques, *Aust. J. B Appl. Sci.* (2015), 372–380.

- [13] H. Zairi, M. Kedir Talha, K. Meddah, et al. FPGA-based system for artificial neural network arrhythmia classification, *Neural Comput & Applic* 32 (2020), 4105–4120. https://doi.org/10.1007/s00521-019-04081-4

- [14] S. Kumbhar, A.D. Darji and H.M. Singapuri, FPGA-Based Implementation of Artifact Suppression and Feature Extraction. In: Patel Z., Gupta S., Kumar Y.B.N. (eds) Advances in VLSI and Embedded Systems. Lecture Notes in Electrical Engineering, vol 676. Springer, Singapore. (2021). https://doi.org/10.1007/978-981-15-6229-7\_10

- [15] V. Tsoutsouras, K. Koliogeorgi, S. Xydis, et al. An Exploration Framework for Efficient High-Level Synthesis of Support Vector Machines: Case Study on ECG Arrhythmia Detection for Xilinx Zynq SoC, *J Sign Process Syst* 88 (2017), 127–147. https://doi.org/10.1007/s11265-017-1230-1

- [16] S. Afifi, H. Gholam Hosseini and R. Sinha, FPGA Implementations of SVM Classifiers: A Review, *SN Comput. Sci.* 1 (2020), 133. https://doi.org/10.1007/s42979-020-00128-9

- [17] Maram Anantha Guptha, Surampudi Srinivasa Rao and Ravindrakumar Selvaraj, An efficient discrete wavelet transform architecture with low power and multiplierless structure for biomedical image processing application, *Harbin Gongye Daxue Xuebao/Journal of Harbin Institute* of Technology 54(2) (2022), 188–196.

- [18] V.M. Senthilkumar and S. Ravindrakumar, A low power and area efficient FinFET based approximate multiplier in 32nm technology. In *Proceedings of International Conference on Soft Computing and Signal Processing* (2019), 1–12.

- [19] V.M. Senthilkumar and S. Ravindrakumar, A low power and area efficient FinFET based approximate multiplier in 32nm technology in Springer-International Conference on Soft Computing and Signal Processing (2018).

- [20] J.R. Albert, et al., Investigation on load harmonic reduction through solar-power utilization in intermittent SSFI using particle swarm, genetic, and modified firefly optimization algorithms, *Journal of Intelligent and Fuzzy System* 42(4) (2022), 4117–4133. DOI:10.3233/JIFS-212559.

- [21] Z. Dokur and T. Ölmez, Heartbeat classification by using a convolutional neural network trained with Walsh functions, *Neural Comput & Applic* 32 (2020), 12515–12534. https://doi.org/10.1007/s00521-020-04709-w

- [22] R. Selvaraj and B. Kanagaraj, A multi-stage adaptive singular value decomposition approach for fetal ECG signal extraction in multichannel input system for prenatal health monitoring, *Asian Journal of Information Technology* **15**(6) (2016): 1049–1055. 10.36478/ajit.2016.1049.1055

- [23] www.intel.com.

- [24] www.xilinx.com.

- [25] Namburu, Anupama, et al., FPGA-Based Deep Learning Models for Analyzing Corona Using Chest X-Ray Images, Mobile Information Systems (Hindawi), SP - 2110785, VL – 2022, https://doi.org/10.1155/2022/2110785